DM9161B

10/100 Mbps Fast Ethernet Physical Layer Single Chip Transceiver

Final 30

Version: DM9161B-12-DS-F01

January 31, 2008

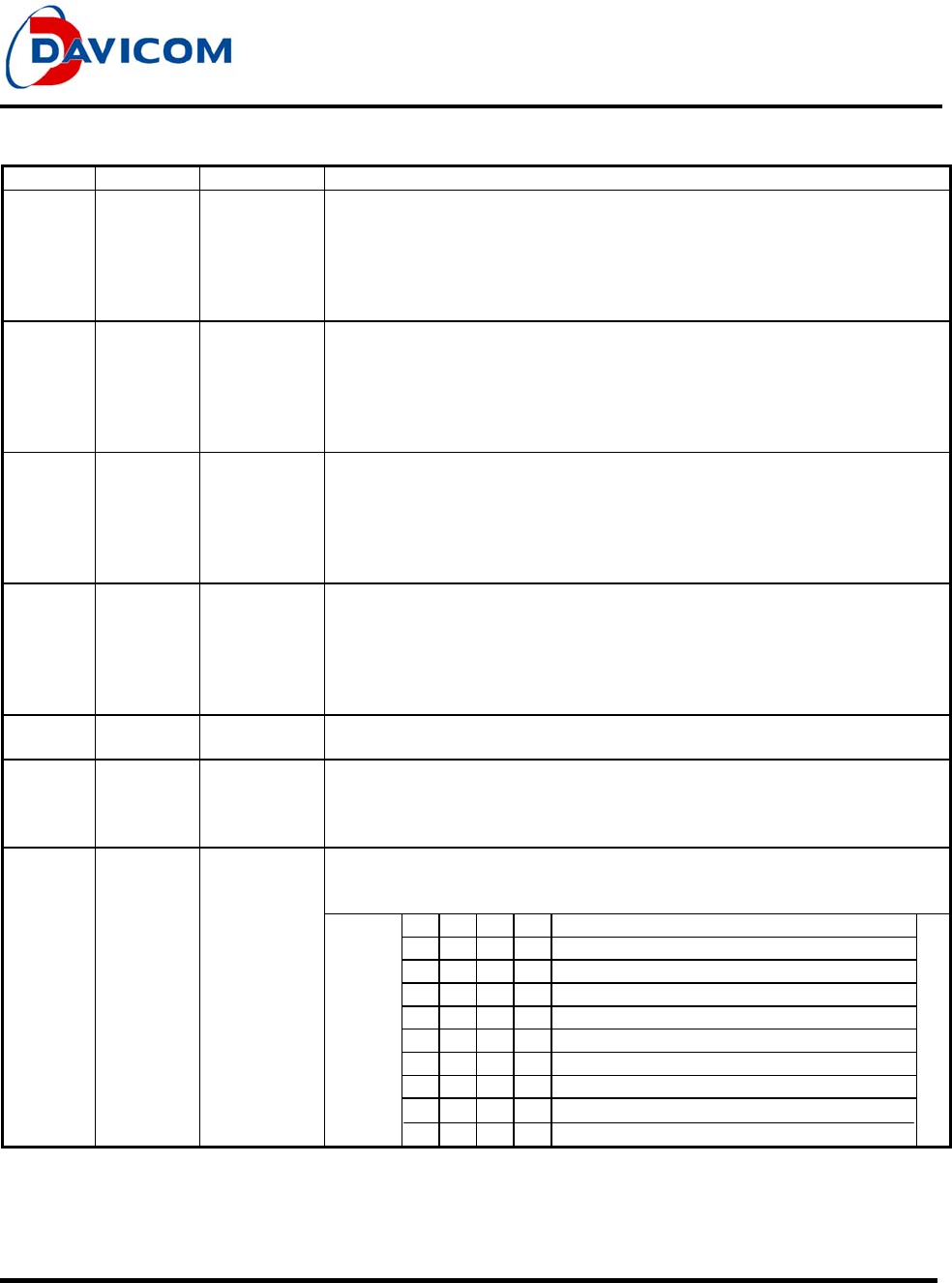

8.9 DAVICOM Specified Configuration and Status Register (DSCSR) - 17

Bit Bit Name Default Description

17.15 100FDX 1, RO 100M Full Duplex Operation Mode

After auto-negotiation is completed, results will be written to this bit. If this

bit is 1, it means the operation 1 mode is a 100M full duplex mode. The

software can read bit [15:12] to see which mode is selected after

auto-negotiation. This bit is invalid when it is not in the auto-negotiation

mode

17.14 100HDX 1, RO 100M Half Duplex Operation Mode

After auto-negotiation is completed, results will be written to this bit. If this

bit is 1, it means the operation 1 mode is a 100M half duplex mode. The

software can read bit [15:12] to see which mode is selected after

auto-negotiation. This bit is invalid when it is not in the auto-negotiation

mode

17.13 10FDX 1, RO 10M Full Duplex Operation Mode

After auto-negotiation is completed, results will be written to this bit. If this

bit is 1, it means the operation 1 mode is a 10M Full Duplex mode. The

software can read bit [15:12] to see which mode is selected after

auto-negotiation. This bit is invalid when it is not in the auto-negotiation

mode

17.12 10HDX 1, RO 10M Half Duplex Operation Mode

After auto-negotiation is completed, results will be written to this bit. If this

bit is 1, it means the operation 1 mode is a 10M half duplex mode. The

software can read bit [15:12] to see which mode is selected after

auto-negotiation. This bit is invalid when it is not in the auto-negotiation

mode

17.11-17.

9

Reserved 0, RO Reserved

Read as 0, ignore on write

17.8-17.4 PHYADR[4

:0]

(PHYADR),

RW

PHY Address Bit 4:0

The first PHY address bit transmitted or received is the MSB of the address

(bit 4). A station management entity connected to multiple PHY entities

must know the appropriate address of each PHY

Auto-negotiation Monitor Bits

These bits are for debug only. The auto-negotiation status will be written to

these bits.

b3 b2 b1 B0

0000In IDLE state

0001Ability match

0010Acknowledge match

0011Acknowledge match fail

0100Consistency match

0101Consistency match fail

0110Parallel detects signal_link_ready

17.3-17.0 ANMB[3:0] 0, RO

0

1

1

0

1

0

1

0

Parallel detects signal_link_ready fail

Auto-negotiation completed successfully