VT1536A Isolated Digital Input/Output SCP 9

completely asynchronous with the VT1415A/19A algorithm execution rate

as set by the Trigger Timer (

TRIG:TIMER command). Long debounce

periods combined with fast Trigger Timer settings would have the algorithm

executing several times for each input debounce-and-latch period.

Conversely, short debounce periods and slow Trigger Timer rates would

allow multiple debounce-and-latches per algorithm execution.

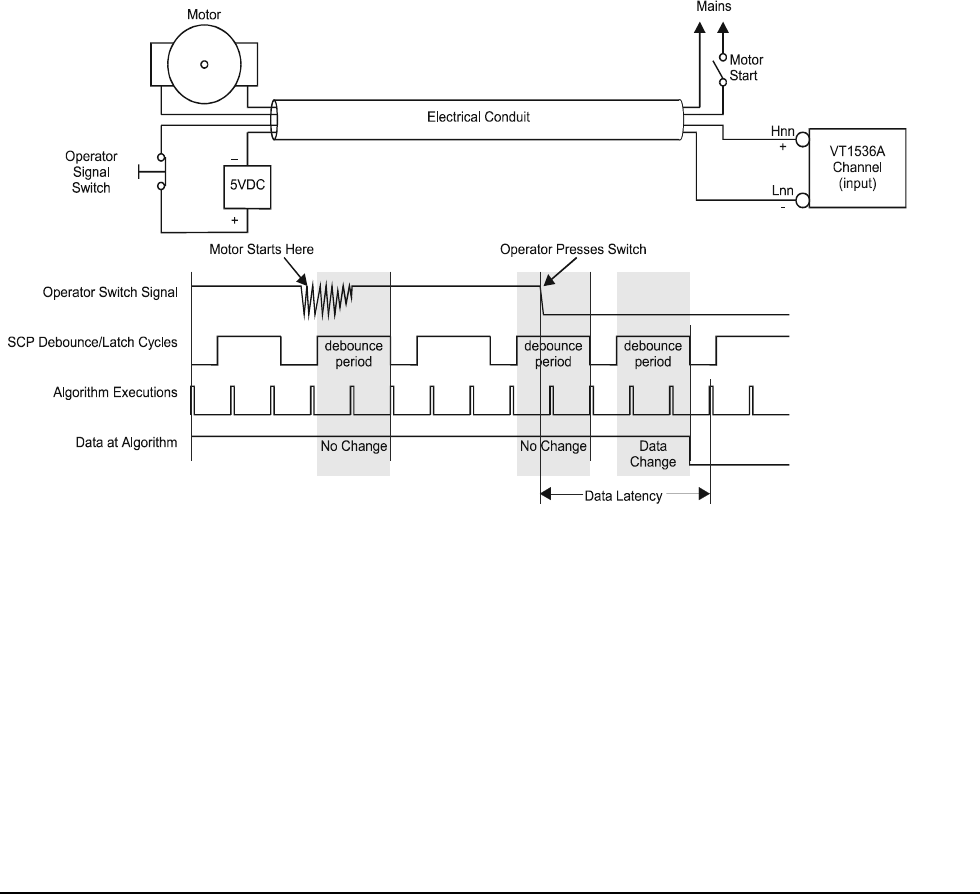

Debounce Example Figure 5 demonstrates the use of debounce. Here we show a system that uses

a digital line to sense a switch an operator would throw to signal the

algorithm to shut down a process. The digital line runs through an electrical

environment that could cause a false shut-down signal when a large motor

starts. The motor start period is at most 0.5 seconds. The algorithm executes

every 100 ms so without debounce it could sense this electrical noise as a

false shut-down signal. If we set the debounce period to 1.228 seconds, the

VT1536A will ignore the motor start-up noise and will only latch signal

states that last as long or longer than the debounce period.

Data Latency With the debounce feature on, the data latency (the time from valid signal

transition to acquisition by the algorithm is up to 1.333 times the debounce

period plus one VT1415A/19A trigger repetition period

(

TRIG:TIM:PERIOD).

With the debounce feature off (INPut:DEBounce 0,(@<ch_list>), the

latency is only the algorithm repetition rate.

Figure 5 Example Using Debounce Feature