Philips Semiconductors Product specification

SA70161.3GHz low voltage fractional-N synthesizer

1999 Nov 04

12

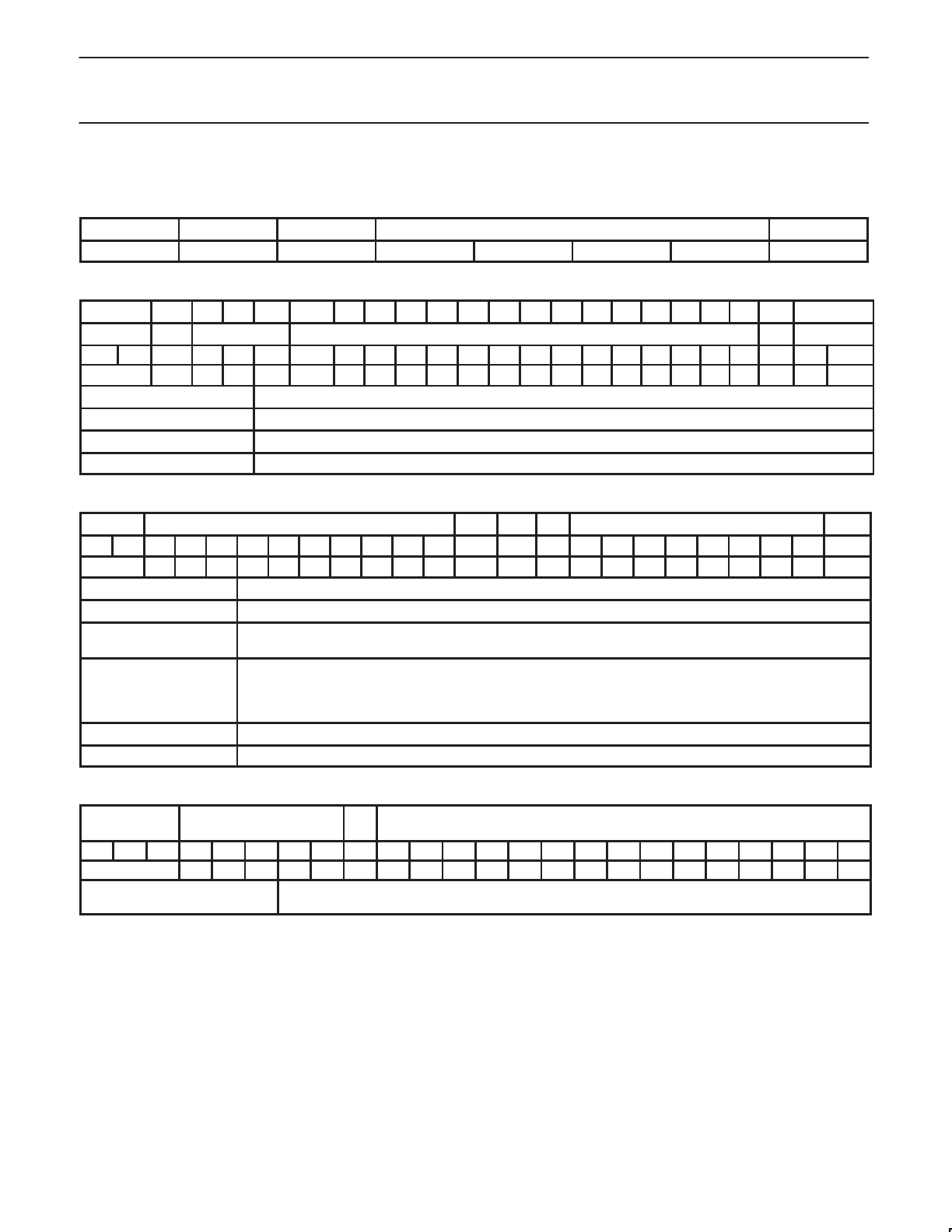

Data format

Table 1. Format of programmed data

LAST IN MSB SERIAL PROGRAMMING FORMAT FIRST IN LSB

p23 p22 p21 p20 ../.. ../.. p1 p0

Table 2. A word, length 24 bits

LAST IN MSB LSB FIRST IN

Address fmod Fractional-N Main Divider ratio Spare

0 0 FM NF2 NF1 NF0 N15 N14 N13 N12 N11 N10 N9 N8 N7 N6 N5 N4 N3 N2 N1 N0 SP1 SP2

Default:

0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 0 0 0

A word select Fixed to 00.

Fractional Modulus select FM 0 = modulo 8, 1 = modulo 5.

Fractional-N Increment NF2..0 Fractional N Increment values 000 to 111.

N-Divider N0..N15, Main divider values 512 to 65535 allowed for divider ratio.

Table 3. B word, length 24 bits

Address

REFERENCE DIVIDER

LOCK

PD CP FRACTIONAL COMPENSATION DAC

SPARE

0 1 R9 R8 R7 R6 R5 R4 R3 R2 R1 R0 LO MAIN CP0 FC7 FC6 FC5 FC4 FC3 FC2 FC1 FC0 SP3

Default: 0 0 0 1 0 1 0 0 0 1 0 0 0 0 1 0 1 0 0 0 0 0

B word select Fixed to 01

R-Divider R0..R9, Reference divider values 4 to 1023 allowed for divider ration.

Charge pump current

Ratio

CP0: Charge pump current ratio, see table of charge pump currents.

Lock detect output L0

0 Main lock detect signal present at the LOCK pin (push/pull).

1 Main lock detect signal present at the LOCK pin (open drain).

When main loop is in power down mode, the lock indicator is low.

Power down Main = 1: power to main divider, reference divider, main charge pumps, Main = 0 to power down.

Fractional Compensation FC7..0 Fractional Compensation charge pump current DAC, values 0 to 255.

Table 4. D word, length 24 bits

Address SYNTHESIZER TEST

BITS

SYNTHESIZER TEST BITS

1 1 0 – – – – – Tspu – – – – – – – – – – – – – – –

Default: 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Tspu: Speed up = 1 Forces the main charge pumps in speed-up mode all the time.

NOTE: All test bits must be set to 0 for normal operation.