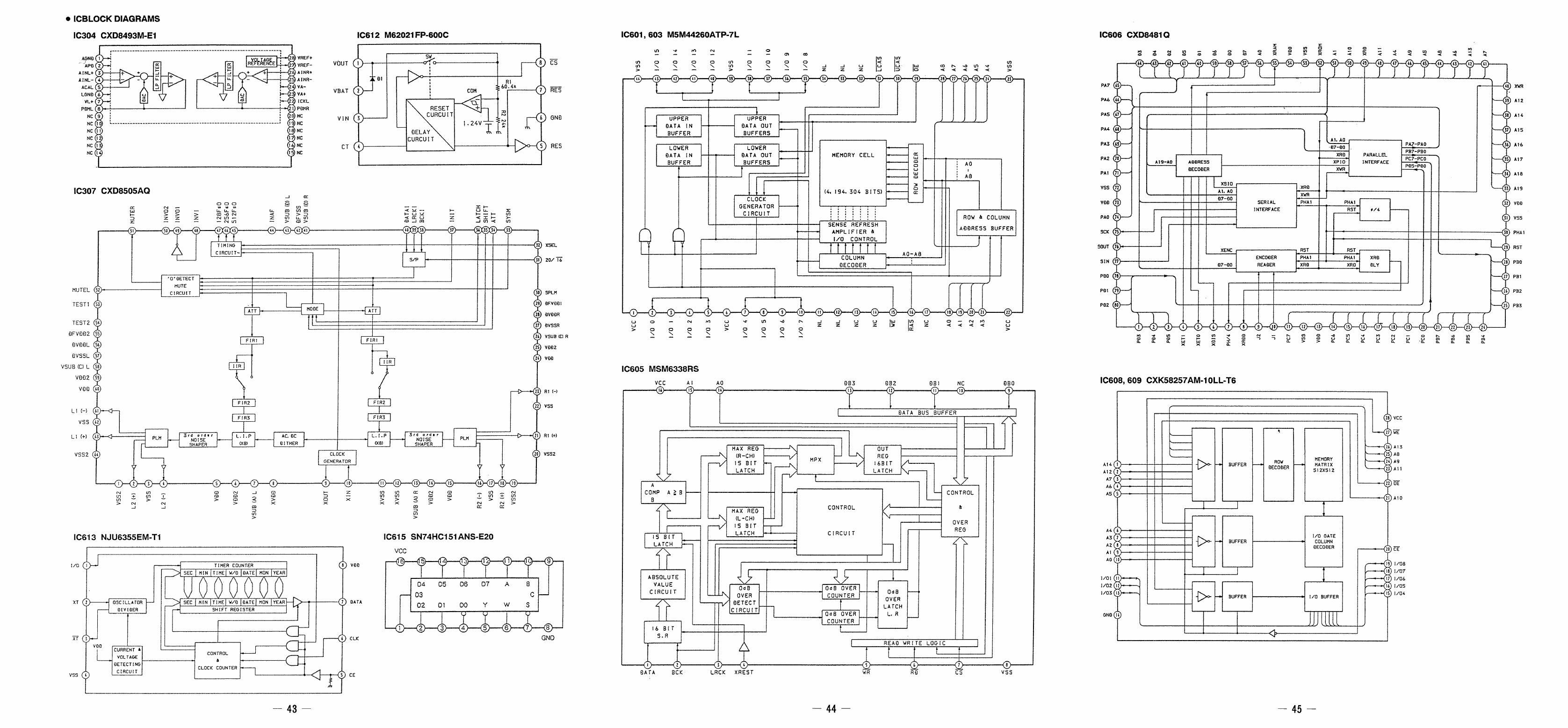

• ICBLOCK DIAGRAMS

IC304

CXD8493M-E1

t~----------------------------------------------------

------------..,

A!lND

~AP-B

A.INl-

ACAl

VlT

P£lML

Ne

Ne

: :

, . '

...

_-

----------

-------

-------------------

--

------

-----

-

--

--

-

----

--

-_.

IC307 CXD8505AQ

TESTZ

8FV8BZ

OVBBL

LI

H

LI

(T)

N

a 0

> >

z z

r-----~·,01------f50

IC613 NJU6355EM·

T1

CURRENT

I;

VOL

rAGE:

£IETfeTlNG

CIRCUIT

>

z

'"

'"

>

N

'"

Q

>

..J

3

PO

::>

If)

>

..J

a:

§

U'J

§

t..L.

p:l

((}

tIl

..:(

~

>

~

z

en

u..

(f)

>

'"

>

'"

'"

>

x

-

43-

>--

::>

o

x

VOUT

VBAT

VIN

CT

z

x

IC612 M62021 FP-60.0C

({)

If)

>

x

({)

If)

>

x

SW

BELAY

eUReUIT

'"

3

PO

::>

({)

>

N

'"

'"

>

'"

'"

>

COM

IC615 SN74HC151ANS·E20

vee

04

03

02

05

01

00

y

RI

60.4'

w

e

s

GNB

RES

flFvnOl

ilVtl£lR

VSUB

((:1

R

GNO

IC601,603

M5M44260ATP-7L

u

u

>

c

a

"

o

"

o

"

IC605 MSM6338RS

vce

AI

"

15

~

A

nB~

CaMP

B

~'r

I

IS BIT

~

LATCH

ABSOLUTE

VALUE

CIRCUIT

11

b

81

T I

S.R

I

U-J

OA

TA

8CK

..,

a

"

AO

"

u

u

>

~

-V

~

r-V

~

-v

MAX

REe>

(R-CH)

15

BIT

LATCH

MAX

REG

(L-CH)

15

BIT

LATCH

t~

OdB

OVER

DETECT

CIRCUIT

,J

.~

lRCK

XREST

o

If)

o

"

f-

~

rv

'---

rr--

h

"

a

"

..J

Z

HPX

..J

Z

u

z

BB3

f

u

z

I~

eBZ

f

I~

u

z

OBI

NC

~

DATA

BUS

BUFFER

uL

~

OUT

REG

A

r-----v

16BIT

LA

TCH

rY--

,

CONTROL

~

CONTROL

&

OVER

CIRCUIT

REG

il

~>

J

OdB

OVER

l-

i-

OoB

-

COUNTER

t

OVER

LATCH

Oa8

OVER

f-

L,

R

COUNTER

-

-

L....-.

REAO

IIR

I

TE

lOGIC

J

t t

t

{-

,-}

IIR

RO

CS

-

44-

u

u

>

OBO

r-

J

-<D--

V55

IC606 CXD8481 Q

PA7 !5

PAb

!!

PAS

!7

PM

II

PA3

"

PA2

7'

PAt

71

VSS

71

va~

73

PAO

7<

Sc<

II

SOUT

11

SIN

11

PDO

71

PDI

7<J

PD2

I.

U

I

M

Q

..

!3

12

1t19-AO

I

I

~

..

..

3

'"

..

..

'"

..

II

4

40

MHlRESS

eECOOER

...

..

59 58

I

I

~

Al.

AO

-

"-

5 I

o

r

w

x

~7

eo

XENe

D7-flO

7

"

..

51

I

..

:E

x

IC608,609

CXK58257AM-10LL-T6

AI4

All

A7

Ab

A5

A4

A3

A2

AI

AO

1/0\

1/02

1/03

I

I

3

,

5

,

7

I

,

"

"

1/

13

"

-

'---

--

:---

'----

{>--

BUFFER

~

-

{>--

BUFFER

~

-

{>-r-

BUFFER

T I

54

55

SERIAL

INTERFACE

£NCQ{lER

REAflER

9

N

.,

•

,

Ra~

51

II

r---

DECODER

...,

"

53

1

"

o

'"

x

52

I

51

<>

..

50

~

·!)7-BO .

XRD

XPIO

C

~

"""

PH

...

1

PHAI J

~

RST

PHAI

XRa

1/

Il

II

MEMORY

-

HATRIX

SI2XSI2

I

I/O

GATE

COLUMN

DECODER

I

I/O

BUFFER

JJJ

lllll

RST

PHAI

XRD

15

on

U

0.

-

45-

19

18

"

PARALLEL

lNTERFACE

..

..

<I

15

PA1-PAO

PB7-PHO

PC7

pea

~O

II

./~

~

XRD

~

alY

11

"

N

U

0.

4

17

['----jl'

vec

AI3

AB

A9

All

['----jlS

~II

'--------(

13

II

II

10

,..---i"

~'8

~"

~II

~IS

Ala

1/08

1/07

1/0b

1/05

1/04

"

U

0.

"

"

I!

11

41

"

"

At2

!I

At4

31

A15

l!

35

A17

3<

AI.

31

At9

1/

vaD

31

VSS

3. PHAl

/,

RST

21

PBO

/7

PBI

II

PB2

2S

PB3

II

21

l!

H