100

State/Timing Modules Specifications and

Characteristics

Agilent Technologies 16760A

Supplemental Specifications and Characteristics (continued)

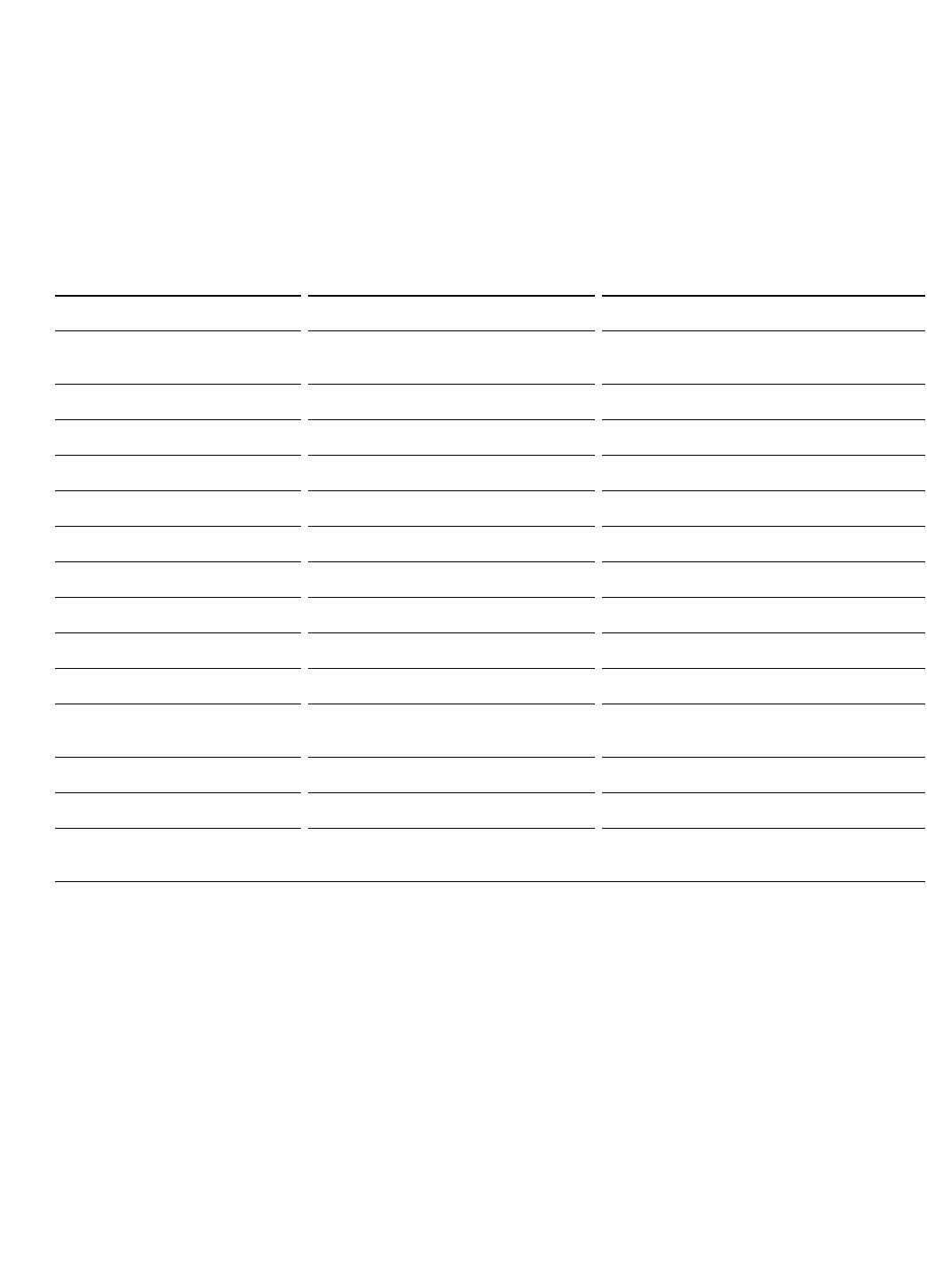

Eye scan mode 1.5 Gb/s mode 800 Mb/s mode

Maximum clock rate 1.5 Gb/s 800 Mb/s

Sample position range relative +5ns to 10 ns -4 ns to +4 ns

to clock

Sample (time) position resolution 12 ps 12 ps

Sample position (time) accuracy +/- (50 ps + 0.01 * sample position) +/- (50 ps + 0.01 * sample position)

Number of channels 16*(number of modules) 34*(number of modules)-1

Input dynamic range -3.0 Vdc to +5.0 Vdc -3.0 Vdc to +5.0 Vdc

Threshold range -3.0 Vdc to +5.0 Vdc -3.0 Vdc to +5.0 Vdc

Threshold resolution 2 mV 2 mV

Threshold accuracy +/-(30 mV + 1% of setting) +/-(30 mV + 1% of setting)

Equivalent rise time [1] 150 ps 150 ps

Equivalent bandwidth [1] 2.33 GHz 2.33 GHz

Minimum detectable pulse width 500 ps 750 ps

at minimum signal amplitude [1]

Jitter 10 ps RMS 10 ps RMS

Noise floor 25 mV p-p 25 mV p-p

Channel-to-channel skew, maximum 100 ps 100 ps

between any two channels

[1] E5378A, E5379A, and E5382A probes only.

Qualified eye scan mode

In the qualified eye scan mode, a

single qualifier input defines what

clock cycles are to be acquired and

what cycles are to be ignored in eye

scan acquisition.

Qualified eye scan is supported in

the 16760A in 800 Mb/s eye scan

mode only. Qualified eye scan is

only available for double-edged clock

(double-data-rate).

Channels available

The following channels are not

available for qualified eye scan

measurements.

Master module, Pod 1

Master module, Pod 2, Bit 0, Bit 14,

Bit 1, Bit 15, Bit 2, K-clock

(the qualifier input itself).

All channels on all boards other than

the master board are available for

qualified eye scans.

Timing

The analyzer samples the qualifica-

tion signal at the beginning of each

clock cycle (i.e. at the first of each

pair of data transfers). The analyzer

can be configured to treat either the

rising edge or the falling edge of the

clock as the first edge of each clock

cycle. The qualifier should remain

stable for the entire duration of

each burst.

The qualifier must be pipelined

(delayed) by one clock cycle before

transmittal to the analyzer.