Altera Corporation 13

GettingOverview

Overview

1

Full Width Register-Indirect with Offset

The LDP, LDS, STP and STS instructions can load or store a full native-

word to or from a register using another register to specify an address,

and an immediate value to specify an offset, in native words, from that

address.

Unlike the LD and ST instructions, which can use any register to specify a

memory address, these instructions may each only use particular registers

for their address. The LDP and STP instructions may each only use the

register %L0, %L1, %L2, or %L3 for their address registers. The LDS and

STS instructions may only use the stack pointer, register %sp (equivalent

to %o6), as their address register. These instructions each take a signed

immediate index value that specifies an offset in native words from the

aligned address pointed in the address register.

Partial Width Register-Indirect with Offset

There are no instructions that read a partial word from memory. To read

a partial word, you must combine a full width indexed register-indirect

read instruction with an extraction instruction, EXT8d, EXT8s, EXT16d

(32-bit Nios CPU only) or EXT16s (32-bit Nios CPU only). The STS8s and

STS16s (Nios 32 only) use an immediate constant to specify a byte or half-

word offset, respectively, from the stack pointer to write the

correspondingly aligned partial width of the source register %r0.

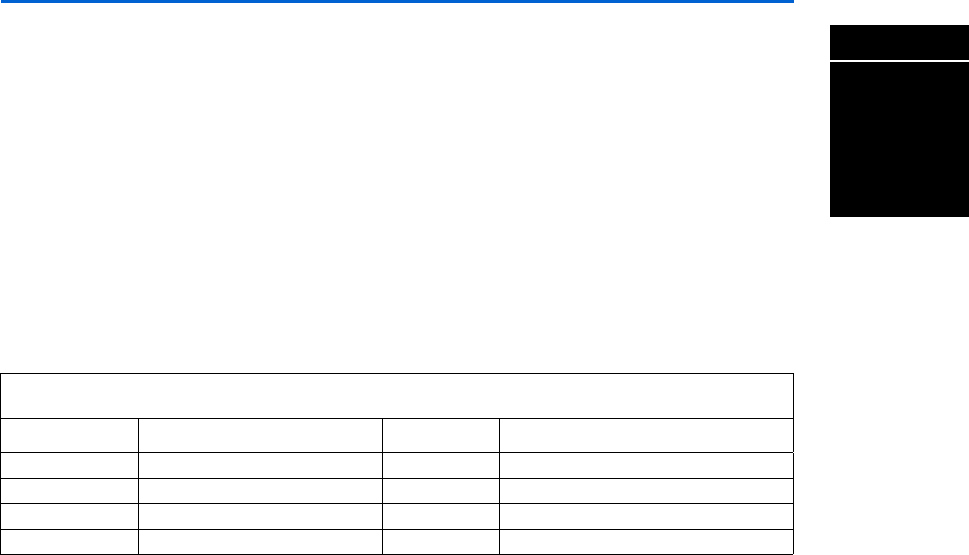

Table 13. Instructions Using Full Width Register-indirect with Offset Addressing

Instruction Address Register Data Register Offset Range without PFX

LDP %L0, %L1, %L2, %L3 Any -16..15 native-words

LDS %sp Any 0..255 native-words

STP %L0, %L1, %L2, %L3 Any -16..15 native-words

STS %sp Any 0..255 native-words