S3C84E5/C84E9/P84E9 INTERRUPT STRUCTURE

5-9

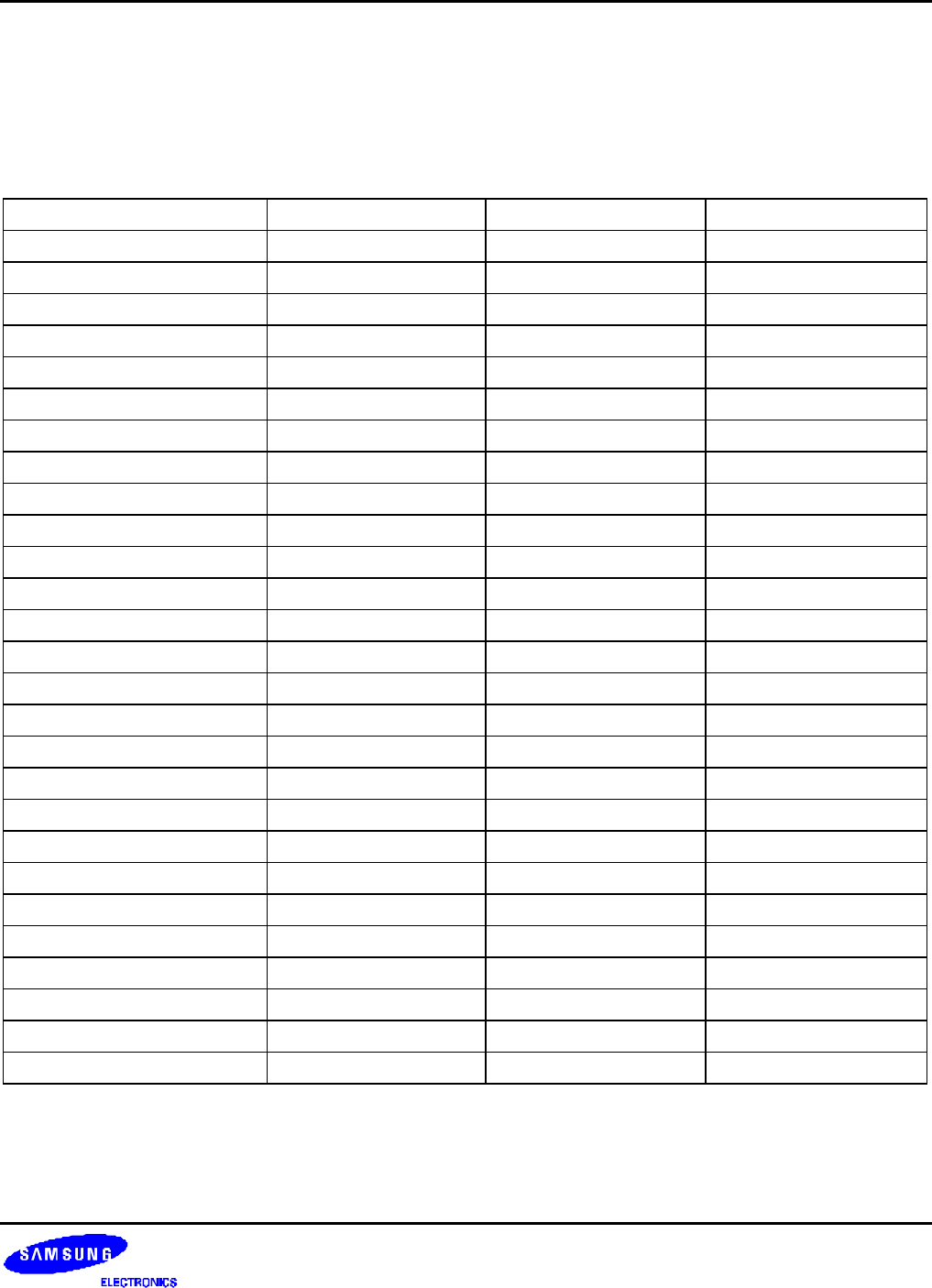

PERIPHERAL INTERRUPT CONTROL REGISTERS

For each interrupt source there is one or more corresponding peripheral control registers that let you control the

interrupt generated by the related peripheral (see Table 5-3).

Table 5-3. Interrupt Source Control and Data Registers

Interrupt Source Interrupt Level Register(s) Location(s) in set1

Timer B underflow IRQ0 TBCON D0H

TBDATAH, TBDATAL D1H, D2H,

Timer A overflow IRQ1 TINTPND E0H, bank 1

Timer A match/capture TACON E1H, bank 1

TADATA E2H, bank 1

TACNT E3H, bank 1

Timer 1(0) match/capture IRQ2 T1DATAH0,T1DATAL0 E4H, E5H, bank 1

Timer 1(0) overflow T1DATAH1,T1DATAL1 E6H, E7H, bank 1

Timer 1(1) match/capture T1CON0, T1CON1 E8H, E9H, bank 1

Timer 1(1) overflow T1CNTH0, T1CNTL0 EAH, EBH, bank 1

T1CNTH1, T1CNTL1 ECH, EDH, bank 1

TINTPND E0H, bank 1

Watch timer IRQ3 WTCON FAH, bank 0

P2.0 external interrupt IRQ4 P2CONL EBH, bank 0

P2.1 external interrupt P2INT ECH, bank 0

P2.2 external interrupt P2INTPND EDH, bank 0

P2.3 external interrupt

P2.4 external interrupt IRQ5 P2CONH EAH, bank 0

P2.5 external interrupt P2INT ECH, bank 0

P2.6 external interrupt P2INTPND EDH, bank 0

P2.7 external interrupt

P4.0 external interrupt IRQ6 P4CONL F1H, bank 0

P4.1 external interrupt P4INT F2H, bank 0

P4.2 external interrupt P4INTPND F3H, bank 0

UART receive/transmit IRQ7 UARTCON F6H, bank 0

UDATA, UARTPND F5H, F4H, bank 0

BRDATAH, BRDATAL EEH, EFH, bank 1