S3C84E5/C84E9/P84E9 ADDRESS SPACES

2-5

REGISTER PAGE POINTER (PP)

The S3C8-series architecture supports the logical expansion of the physical 512-byte internal register file (using an

8-bit data bus) into as many as 2 separately addressable register pages. Page addressing is controlled by the

register page pointer (PP, DFH). In the S3C84E5/C84E9/P84E9 microcontroller, a paged register file expansion is

implemented for data registers, and the register page pointer must be changed to address other pages.

After a reset, the page pointer's source value (lower nibble) and the destination value (upper nibble) are always

"0000", automatically selecting page 0 as the source and destination page for register addressing.

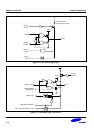

Register Page Pointer (PP)

DFH ,Set 1, R/W

LSBMSB .7 .6 .5 .4 .3 .2 .1 .0

Destination register page selection bits:

Destination: Page 0

Source register page selection bits:

Source: Page 0

NOTE:

A hardware reset operation writes the 4-bit destination and source values shown

above to the register page pointer. These values should be modified to other

pages.

0000 0000

Destination: Page 1 Source: Page 10001 0001

Figure 2-3. Register Page Pointer (PP)