INTERRUPT STRUCTURE S3C84E5/C84E9/P84E9

5-10

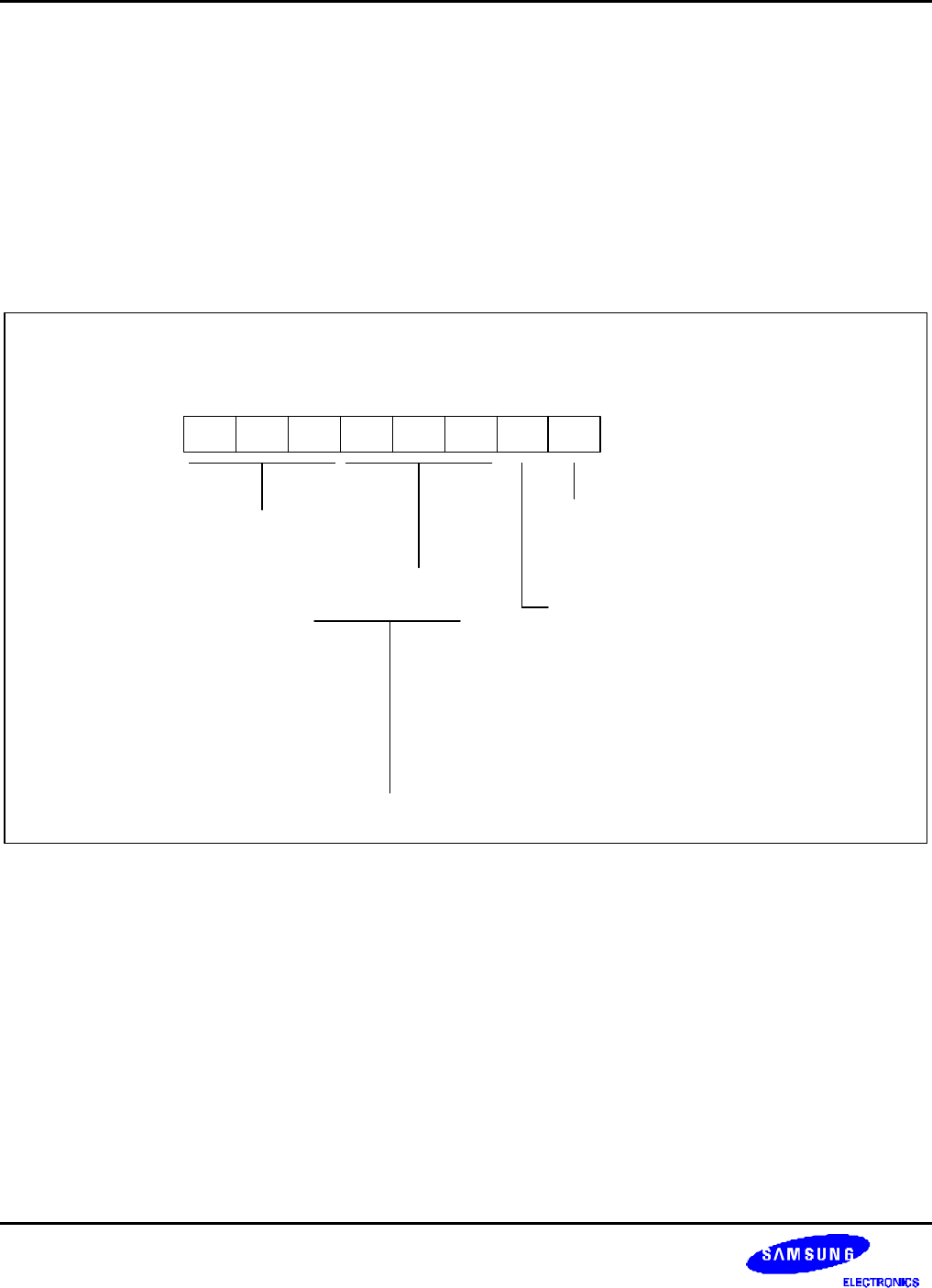

SYSTEM MODE REGISTER (SYM)

The system mode register, SYM (set 1, DEH), is used to globally enable and disable interrupt processing (see

Figure 5-5).

A reset clears SYM.0 to "0".

The instructions EI and DI enable and disable global interrupt processing, respectively, by modifying the bit 0 value of

the SYM register. In order to enable interrupt processing an Enable Interrupt (EI) instruction must be included in the

initialization routine, which follows a reset operation. Although you can manipulate SYM.0 directly to enable and

disable interrupts during the normal operation, it is recommended to use the EI and DI instructions for this purpose.

System Mode Register (SYM)

DEH, Set 1, R/W

.7 .6 .5 .4 .3 .2 .1 .0MSB LSB

Global interrupt enable bit:

0 = Disable all interrupts processing

1 = Enable all interrupts processing

Fast interrupt enable bit:

0 = Disable fast interrupts processing

1 = Enable fast interrupts processing

Fast interrupt level

selection bits:

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

IRQ0

IRQ1

IRQ2

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

Not used for the S3C84E5/C84E9/

P84E9

Figure 5-5. System Mode Register (SYM)