RESET and POWER-DOWN S3C84E5/C84E9/P84E9

8-2

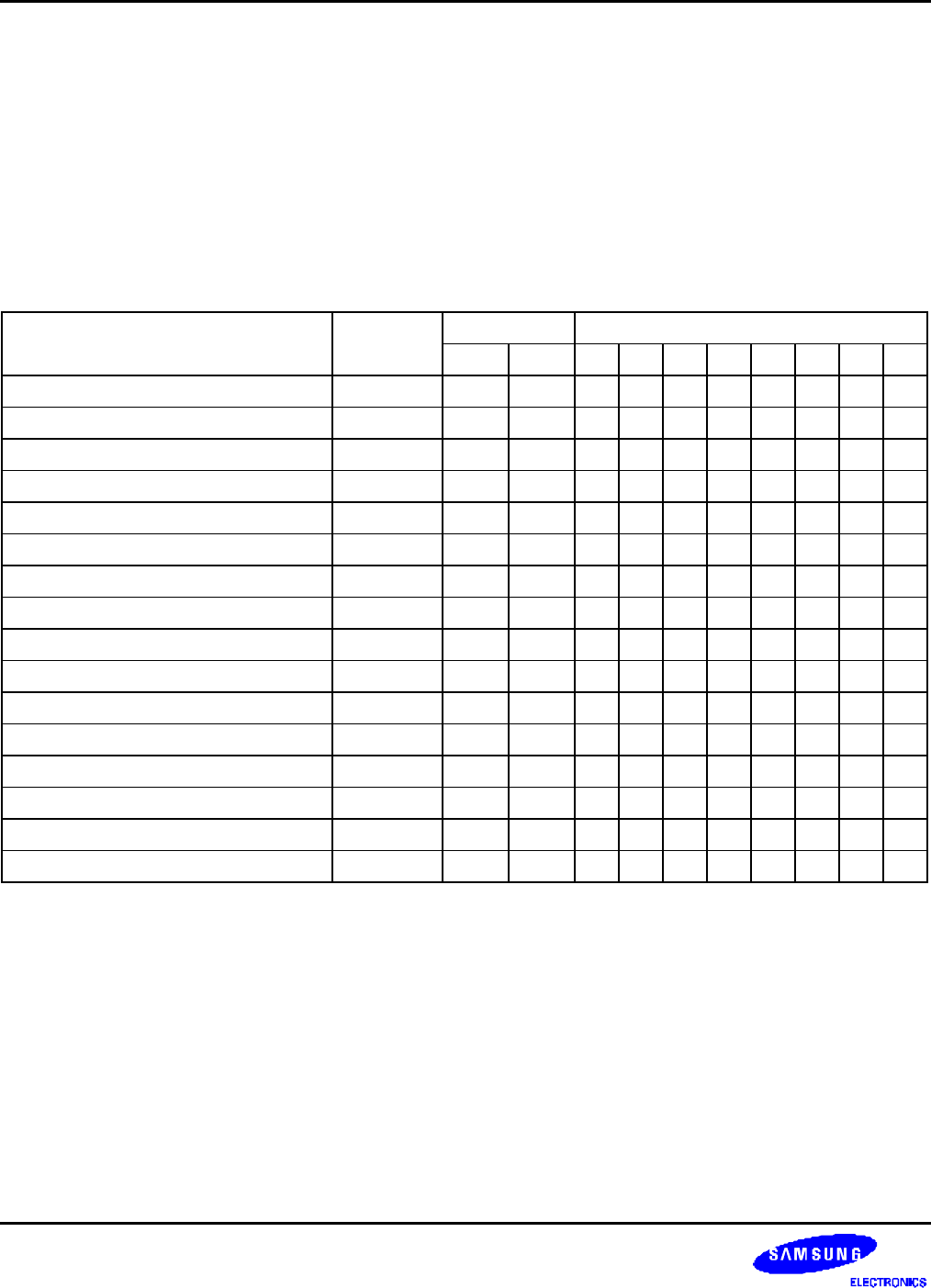

HARDWARE RESET VALUES

Table 8-1, 8-2, and 8-3 list the reset values for CPU and system registers, peripheral control registers, and peripheral

data registers following a reset operation. The following notation is used to represent reset values:

— A "1" or a "0" shows the reset bit value as logic one or logic zero, respectively.

— An "x" means that the bit value is undefined after a reset.

— A dash ("–") means that the bit is either not used or not mapped, but read 0 is the bit value.

Table 8-1. S3C84E5/C84E9/P84E9 Set 1 Register Values After RESET

Register Name Mnemonic Address Bit Values After RESET

Dec Hex 7 6 5 4 3 2 1 0

Timer B control register TBCON 208 D0H 0 0 0 0 0 0 0 0

Timer B data register (high byte) TBDATAH 209 D1H 1 1 1 1 1 1 1 1

Timer B data register (low byte) TBDATAL 210 D2H 1 1 1 1 1 1 1 1

Basic timer control register BTCON 211 D3H 0 0 0 0 0 0 0 0

Clock control register CLKCON 212 D4H 0 0 0 0 0 0 0 0

System flags register FLAGS 213 D5H x x x x x x 0 0

Register pointer 0 RP0 214 D6H 1 1 0 0 0 – – –

Register pointer 1 RP1 215 D7H 1 1 0 0 1 – – –

Stack pointer (high byte) SPH 216 D8H x x x x x x x x

Stack pointer (low byte) SPL 217 D9H x x x x x x x x

Instruction pointer (high byte) IPH 218 DAH x x x x x x x x

Instruction pointer (low byte) IPL 219 DBH x x x x x x x x

Interrupt request register IRQ 220 DCH 0 0 0 0 0 0 0 0

Interrupt mask register IMR 221 DDH x x x x x x x x

System mode register SYM 222 DEH 0 0 0 x x x 0 0

Register page pointer PP 223 DFH 0 0 0 0 0 0 0 0