www.ti.com

5.4PeripheralSettingsControlRegister(PER_SET_CNTL)

SRIORegisters

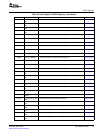

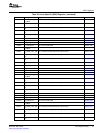

Figure60.PeripheralSettingsControlRegister(PER_SET_CNTL)

31-2726252423-2120-1817-16

ReservedSW_MLOOPBOOTReservedTX_PRI2_WMTX_PRI1_WM

EM_SBACK_COM

LEEP_PLETE

OVER

RIDE

R-0x00RW-RW-RW-R-0x00RW-0x01RW-0x02

0x010x000x00

LEGEND:R=Readonly;-n=valueafterreset

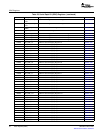

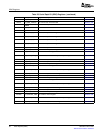

1514-1211-987-43210

TX_PTX_PRI0_WMCBA_TRANS_PRI1X_MPRESCALER_SELECTENPLLENPLLENPLLENPLL

RI1_WODE4321

M

RW-RW-0x03RW-0x00RW-RW-0x0000RW-RW-RW-RW-

0x020x000x000x000x000x00

LEGEND:R=Readonly;-n=valueafterreset

Table31.PeripheralSettingsControlRegister(PER_SET_CNTL)FieldDescriptions

BitFieldValueDescription

31-27ReservedReserved

26SW_MEM_SLEESoftwareMemorySleepOverride

P_OVERRIDE

0bMemoriesareputinsleepmodewhileinshutdown

1bMemoriesarenotputinsleepmodewhileinshutdown

25LOOPBACKLoopbackmode.

0bNormaloperation

1bLoopbackmode.Transmitdatatoreceiveonthesameport.Packetdataisloopedbackinthe

digitaldomainbeforetheSERDESmacros.

24BOOT_COMPLEControlsabilitytowriteanyregisterduringinitialization.Italsoincludesreadonlyregistersduring

TEnormalmodeofoperationthathaveapplicationdefinedresetvalue.

0bWritetoreadonlyregistersenabled

1bWritetoreadonlyregistersdisabled.Usuallytheboot_completeisassertedonceafterresetto

definepoweronconfiguration.

23-21ReservedReserved

20-18TX_PRI2_WMTransmitcreditthreshold.SetstherequirednumberoflogicallayerTXbuffersneededtosend

priority2packetsacrosstheUDIinterface.Thisisvalidforallportsin1Xmodeonly.

Requiredbuffercountfortransmitcreditthreshold2value(TX_PRI2_WM):

•000→8,7,6,5,4,3,2,1

•001→8,7,6,5,4,3,2

•010→8,7,6,5,4,3

•011→8,7,6,5,4

•100→8,7,6,5

•101→8,7,6

•110→8,7

•111→8

SPRU976–March2006SerialRapidIO(SRIO)101

SubmitDocumentationFeedback