www.ti.com

4.5InterruptGeneration

4.6InterruptPacing

InterruptConditions

LSUbitswithintheICSRarelogicallygroupedforagivencoreandORdtogetherintoasinglebitofthe

decoderegister.Similarly,theError/Reset/SpecialeventbitswithintheICSRareORdtogetherintoa

singlebitofthedecoderegister.Wheneitherofthesebitsaresetinthedecoderegister,theCPUmust

makeadditionalreadstothecorrespondingICSRstodeterminethatexactinterruptsource.Itis

recommendedtoarrangetheDoorbellICSRspercore,sothattheCPUcandeterminetheDoorbell

interruptsourcefromasinglereadofthedecoderegister.IftheRXandTXCPPIqueuesareassigned

orthogonallytodifferentcores,theCPUcandeterminetheCPPIinterruptsourcefromasinglereadofthe

decoderegistersaswell.Theonlyexceptiontothisisbit31and30ofthedecoderegister(TXandRX

CPPIQueues19and18)whichareORdwiththeLSUandErrorbit,respectively.

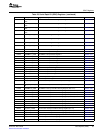

Figure56.INTDSTn_DecodeInterruptStatusDecodeRegister

31302928272625242322212019181716

ISDR3ISDR3ISDR2ISDR2ISDR2ISDR2ISDR2ISDR2ISDR2ISDR2ISDR2ISDR2ISDR1ISDR1ISDR1ISDR1

1098765432109876

R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0

1514131211109876543210

ISDR1ISDR1ISDR1ISDR1ISDR1ISDR1ISDR9ISDR8ISDR7ISDR6ISDR5ISDR4ISDR3ISDR2ISDR1ISDR0

543210

R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0

LEGEND:R=Read,W=Write,n=valueatreset

Offsets:

•INTDST0–0x0300

•INTDST1–0x0304

•INTDST2–0x0308

•INTDST3–0x030C

•INTDST4–0x0310

•INTDST5–0x0314

•INTDST6–0x0318

•INTDST7–0x031C

Interruptsaretriggeredona0-to-1logic-signaltransition.Regardlessoftheinterruptsources,thephysical

interruptsaresetonlywhenthetotalnumberofsetICSRbitstransitionsfromnonetooneormore.The

peripheralisresponsibleforsettingthecorrectbitwithintheICSR.TheICRRregistermapsthepending

interruptrequesttotheappropriatephysicalinterruptline.ThecorrespondingCPUisinterruptedand

readstheISDRandICSRregisterstodeterminetheinterruptsourceandappropriateaction.Interrupt

generationisgovernedbytheinterruptpacingdiscussedSection4.6.

Therateatwhichaninterruptcanbegeneratediscontrollableforeachphysicalinterruptdestination.Rate

controlisimplementedwithaprogrammabledown-counter.Theloadvalueofthecounteriswrittenbythe

CPUintotheappropriateinterruptratecontrolregister(seeFigure57).Thecounterreloadsand

immediatelystartsdown-countingeachtimetheCPUwritestheseregisters.Whentheratecontrolcounter

registeriswritten,andthecountervaluereacheszero(notethattheCPUmaywritezeroimmediatelyfor

azerocount),theinterruptpulsegenerationlogicisallowedtofireasinglepulseifanybitsinthe

correspondingICSRregisterbitsareset(orbecomesetafterthezerocountisreached).Thecounter

remainsatzero.Whenthesinglepulseisgenerated,thelogicwillnotgenerateanotherpulse,regardless

ofinterruptstatuschanges,untiltheratecontrolcounterregisteriswrittenagain.Ifinterruptpacingisnot

desiredforaparticularINTDST,theCPUmuststillwrite0x00000000intotheINTDSTn_RATE_CNTL

registerafterclearingthecorrespondingICSRbitstoacknowledgethephysicalinterrupt.IfanICSRisnot

mappedtoaninterruptdestination,pendinginterruptbitswithintheICSRmaintaincurrentstatus.Once

enabled,theinterruptlogicre-evaluatesallpendinginterruptsandre-pulsestheinterruptsignalifany

interruptconditionsarepending.Thedown-counterisbasedontheDMAclockcycle.

SPRU976–March2006SerialRapidIO(SRIO)85

SubmitDocumentationFeedback