www.ti.com

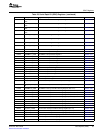

31 30 29 28 27 26 25 24 23 22 21 20 19 1618 17

LSU

Error, reset and special event

Tx CPPI [15:0]

Rx CPPI [15:0]

ISDR bits:

15ISDR bits: 14 13 12 11 6810 9 7 5 4 3 2 01

Doorbell 0 [15:0]

Doorbell 1 [15:0]

Doorbell 3 [15:0]

Doorbell 2 [15:0]

29

29

29

29

29

29

29

29

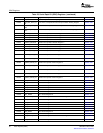

Interrupt Status

Decode Registers

INTDST0

INTDST1

INTDST2

INTDST3

INTDST4

INTDST5

INTDST6

INTDST7

TX CPPI ICRR

TX CPPI ICRR

TX CPPI ICSR

RX CPPI ICSR

2

2

0

0

1

1

2

2

3

3

4

4

5

5

6

6

7

7

InterruptConditions

Figure54.SharingofISDRBits

Asanexample,ifbit29oftheISDRisset,thisindicatesthatthereisapendinginterruptoneithertheTX

CPPIqueue2orRXCPPIqueue2.Figure55illustratesthedecoderouting.

Figure55.ExampleDiagramofInterruptStatusDecodeRegisterMapping

84SerialRapidIO(SRIO)SPRU976–March2006

SubmitDocumentationFeedback