www.ti.com

4.7InterruptHandling

InterruptConditions

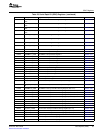

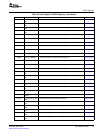

Figure57.INTDSTn_RATE_CNTLInterruptRateControlRegister

310

32-bitCountDownValue

R/W-0

LEGEND:R=Read,W=Write,n=valueatreset

Offsets:

•INTDST0–0x0320

•INTDST1–0x0324

•INTDST2–0x0328

•INTDST3–0x032C

•INTDST4–0x0330

•INTDST5–0x0334

•INTDST6–0x0338

•INTDST7–0x033C

InterruptsareeithersignaledexternallythroughRapidIOpackets,orinternallybystatemachinesinthe

peripheral.CPUservicinginterruptsaresignaledexternallybytheDOORBELLRapidIOpacketinDirect

I/Omode,orinternallybytheCPPImodule(describedinsection8)inthemessagepassingmode.Error

Statusinterruptsaresignaledwhenerrorcountinglogicwithintheperipheralhavereachedtheir

thresholds.Ineithercase,itistheperipheralthatsignalstheinterruptandsetsthecorrespondingstatus

bits.

WhentheCPUisinterrupted,itreadstheICSRregisterstodeterminethesourceoftheinterruptand

appropriateactiontotake.Forexample,ifitisaDOORBELLinterrupt,theCPUwillreadfromanL2

addressthatisspecifiedbyitscircularbufferreadpointerthatismanagedbysoftware.Theremaybe

morethanonecircularbufferforeachcore.Thecorrectcircularbuffertoreadfromandincrement

dependsonthebitsetintheICSRregister.TheCPUthenclearsthestatusbit.

ForErrorStatusinterrupts,theperipheralmustindicatetoalltheCPUsthatoneofthelinkportshas

reachedtheerrorthreshold.Inthiscase,theperipheralsetsthestatusbitindicatingdegradedorfailed

limitshavebeenreached,andaninterruptisgeneratedtoeachcorethroughtheICRRmapping.The

corescanthenscantheICSRregisterstodeterminetheportwiththeerrorproblems.Furtheractioncan

thenbetakenasdeterminedbytheapplication.

InterruptHandler

temp1=SRIO_REGS->TX_CPPI_ICSR;

if((temp1&0x00000001)==0x00000001)

{

SRIO_REGS->Queue0_TxDMA_CP=(int)TX_DESCP0_0;

}

temp2=SRIO_REGS->RX_CPPI_ICSR;

if((temp2&0x00000001)==0x00000001)

{

SRIO_REGS->Queue0_RXDMA_CP=(int)RX_DESCP0_0;

}

interruptStatus[0]=SRIO_REGS->DOORBELL3_ICSR;

interruptStatus[1]=SRIO_REGS->DOORBELL3_ICCR;

interruptStatus[2]=SRIO_REGS->LSU_ICSR;

interruptStatus[3]=SRIO_REGS->LSU_ICCR;

interruptStatus[4]=SRIO_REGS->DOORBELL3_ICRR;

interruptStatus[5]=SRIO_REGS->DOORBELL3_ICRR2;

interruptStatus[6]=SRIO_REGS->LSU_ICRR;

interruptStatus[7]=SRIO_REGS->LSU_ICRR2;

interruptStatus[8]=SRIO_REGS->INTDST0_Decode;

interruptStatus[9]=SRIO_REGS->ERR_RST_EVNT_ICRR;

interruptStatus[10]=SRIO_REGS->INTDST0_Rate_CNTL;

86SerialRapidIO(SRIO)SPRU976–March2006

SubmitDocumentationFeedback