www.ti.com

SRIORegisters

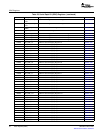

Table31.PeripheralSettingsControlRegister(PER_SET_CNTL)FieldDescriptions(continued)

BitFieldValueDescription

17-15TX_PRI1_WMTransmitcreditthreshold.SetstherequirednumberoflogicallayerTXbuffersneededtosend

priority1packetsacrosstheUDIinterface.Thisisvalidforallportsin1Xmodeonly.

Requiredbuffercountfortransmitcreditthreshold1valueTX_PRI1_WM:

•000→8,7,6,5,4,3,2,1

•001→8,7,6,5,4,3,2

•010→8,7,6,5,4,3

•011→8,7,6,5,4

•100→8,7,6,5

•101→8,7,6

•110→8,7

•111→8

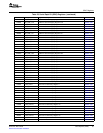

14-12TX_PRI0_WMTransmitcreditthreshold.SetstherequirednumberoflogicallayerTXbuffersneededtosend

priority0packetsacrosstheUDIinterface.Thisisvalidforallportsin1Xmodeonly.

Requiredbuffercountfortransmitcreditthreshold0valueTX_PRI0_WM:

•000→8,7,6,5,4,3,2,1

•001→8,7,6,5,4,3,2

•010→8,7,6,5,4,3

•011→8,7,6,5,4

•100→8,7,6,5

•101→8,7,6

•110→8,7

•111→8

11-9CBA_TRANS_PRVBUStransactionpriority.000b–HighestPriority…111b–LowestPriority.

I

81X_MODEThisregisterbitdeterminestheUDIbufferingsetup(priorityversusport).

0bUDIbuffersareprioritybased

1bUDIbuffersareportbased.Thismodemustbeselectedwhenusingmorethanone1Xport

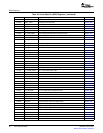

7-4PRESCALER_SEInternalfrequencyprescaler,usedtodrivetherequesttoresponsetimers.These4bitsarethe

LECTprescalerreloadvalueallowingdivisionoftheDMAclockbyarangefrom1upto16.Setting

shouldreflectthedeviceDMAfrequency.

0000bSetstheinternalclockfrequencyMin44.7andMax89.5

0001bSetstheinternalclockfrequencyMin89.5andMax179.0

0010bSetstheinternalclockfrequencyMin134.2andMax268.4

0011bSetstheinternalclockfrequencyMin180.0andMax360.0

0100bSetstheinternalclockfrequencyMin223.7andMax447.4

0101bSetstheinternalclockfrequencyMin268.4andMax536.8

0110bSetstheinternalclockfrequencyMin313.2andMax626.4

0111bSetstheinternalclockfrequencyMin357.9andMax715.8

1000bsetstheinternalclockfrequencyMin402.7andMax805.4

1001bSetstheinternalclockfrequencyMin447.4andMax894.8

1010bSetstheinternalclockfrequencyMin492.1andMax984.2

1011bSetstheinternalclockfrequencyMin536.9andMax1073.8

1100bSetstheinternalclockfrequencyMin581.6andMax1163.2

1101bSetstheinternalclockfrequencyMin626.3andMax1252.6

1110bSetstheinternalclockfrequencyMin671.1andMax1342.2

1111bSetstheinternalclockfrequencyMin715.8andMax1431.6

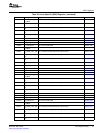

3ENPLL4DrivesSERDESMacro4PLLEnablesignal

0bDisablesmacro4PLL

1bEnablesmacro4PLL

102SerialRapidIO(SRIO)SPRU976–March2006

SubmitDocumentationFeedback