80386

PRIVILEGE

LEVEL

0

(HIGHEST)

PRIVILEGE

LEVEL 3

F=--.J

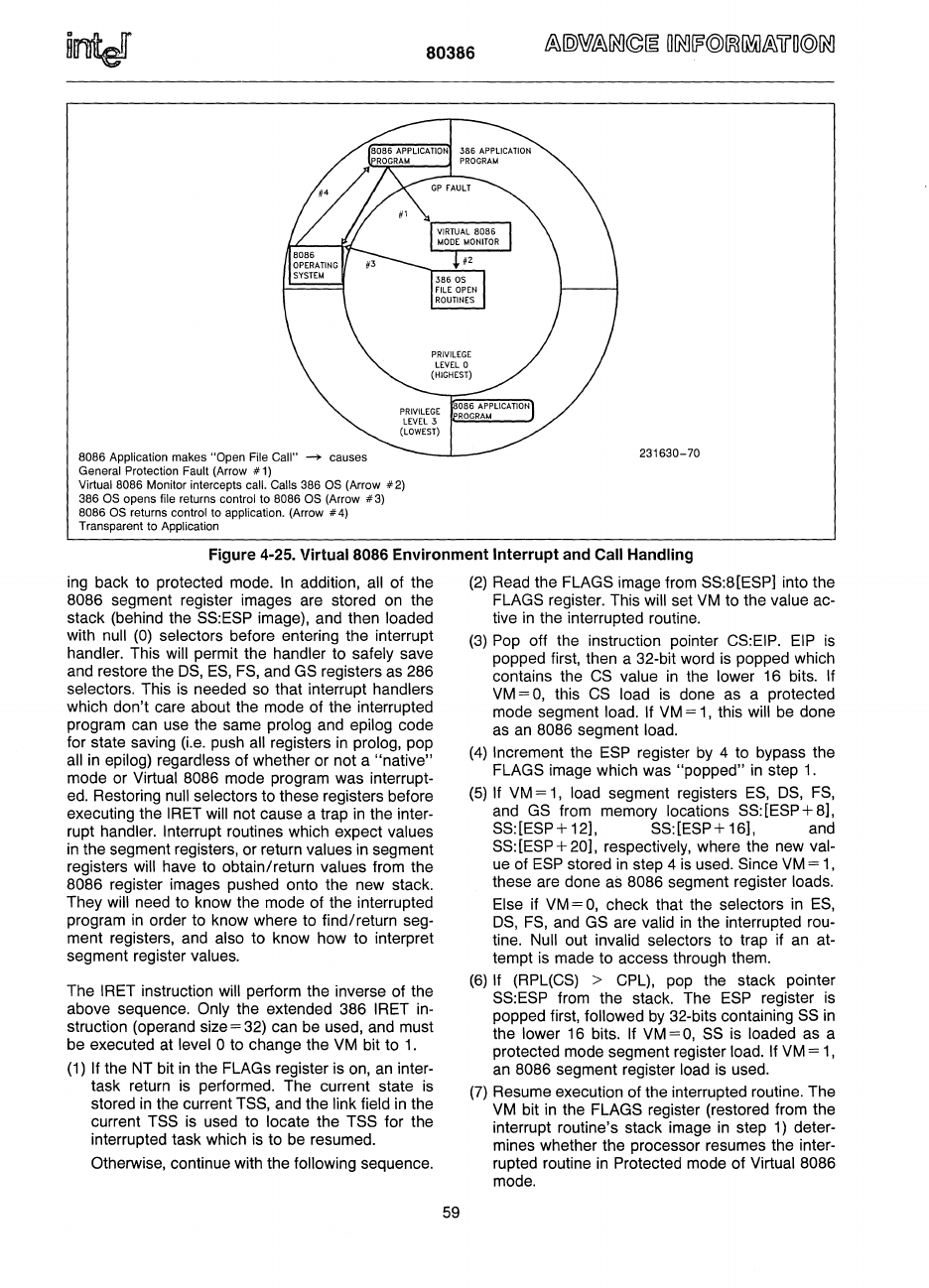

8086 Application makes ··Open File Call"

->

causes

General Protection Fault (Arrow #1)

(LOWEST)

Virtual 8086 Monitor intercepts call. Calls 386 as (Arrow #

2)

386 as opens file returns control to 8086 as (Arrow #

3)

8086 as returns control to application. (Arrow

#4)

Transparent to Application

231630-70

Figure 4·25. Virtual 8086 Environment

Interrupt

and Call Handling

ing

back to protected mode.

In

addition, all of the

(2)

Read the FLAGS image from SS:8[ESP] into the

8086 segment register images are stored

on

the FLAGS register. This will set

VM

to the value ac-

stack (behind the

SS:ESP image), and then loaded tive

in

the interrupted routine.

with

null

(0)

selectors before entering the interrupt

(3)

Pop

off the instruction pointer CS:EIP.

EIP

is

handler. This will permit the handler to safely save popped first, then a 32-bit word

is

popped which

and restore the

OS,

ES,

FS,

and

GS

registers

as

286 contains the

CS

value

in

the lower 16 bits.

If

selectors. This

is

needed

so

that interrupt handlers

VM

=

0,

this

CS

load

is

done

as

a protected

which don't care about the mode of the interrupted mode segment load.

If

VM

=

1,

this will

be

done

program can

use

the same prolog and epilog code

as

an

8086 segment load.

for state saving

(i.e.

push all registers

in

prolog, pop

(4)

Increment the

ESP

register

by

4 to bypass the

all

in

epilog) regardless of whether or not a "native" FLAGS image which was "popped"

in

step

1.

mode or Virtual 8086 mode program was interrupt-

ed.

Restoring null selectors to these registers before

(5)

If

VM

=

1,

load segment registers

ES,

OS,

FS,

executing the IRET will not cause a trap

in

the inter-

and

GS

from memory locations SS:[ESP+ 8],

rupt handler.

Interrupt routines which expect values

SS:

[ESP + 12],

SS:

[ESP

+ 16], and

in

the segment registers, or return values

in

segment

SS:

[ESP

+ 20], respectively, where the new val-

registers

will have

to

obtain/return values from the

ue

of

ESP

stored

in

step 4

is

used. Since

VM

=

1,

8086 register images pushed onto the new stack. these are done as 8086 segment register loads.

They

will need to know the mode of the interrupted Else if

VM

=

0,

check that the selectors

in

ES,

program

in

order to know where

to

find/return seg-

OS,

FS,

and

GS

are valid

in

the interrupted rou-

ment registers, and also to know how to interpret tine.

Null out invalid selectors to trap if

an

at-

segment register values. tempt

is

made to access through them.

The

IRET instruction will perform the inverse of the

above sequence.

Only the extended 386 IRET in-

struction (operand size=32) can

be

used, and must

be executed

at

level 0 to change the

VM

bit to

1.

(1)

If the NT bit

in

the FLAGs register

is

on,

an

inter-

task return

is

performed. The current state

is

stored

in

the current

TSS,

and the link field

in

the

current

TSS

is

used

to

locate the TSS for the

interrupted task which

is

to

be

resumed.

Otherwise, continue with the

following sequence.

59

(6)

If

(RPL(CS) >

CPL),

pop the stack pointer

SS:ESP

from the stack. The

ESP

register

is

popped first, followed

by

32-bits containing

SS

in

the lower 16 bits.

If

VM

=

0,

SS

is

loaded as a

protected mode segment register load.

If

VM

=

1,

an

8086 segment register load

is

used.

(7)

Resume execution of the interrupted routine. The

VM

bit

in

the FLAGS register (restored from the

interrupt routine's stack image

in

step

1)

deter-

mines whether the processor resumes the inter-

rupted routine

in

Protected mode of Virtual 8086

mode.