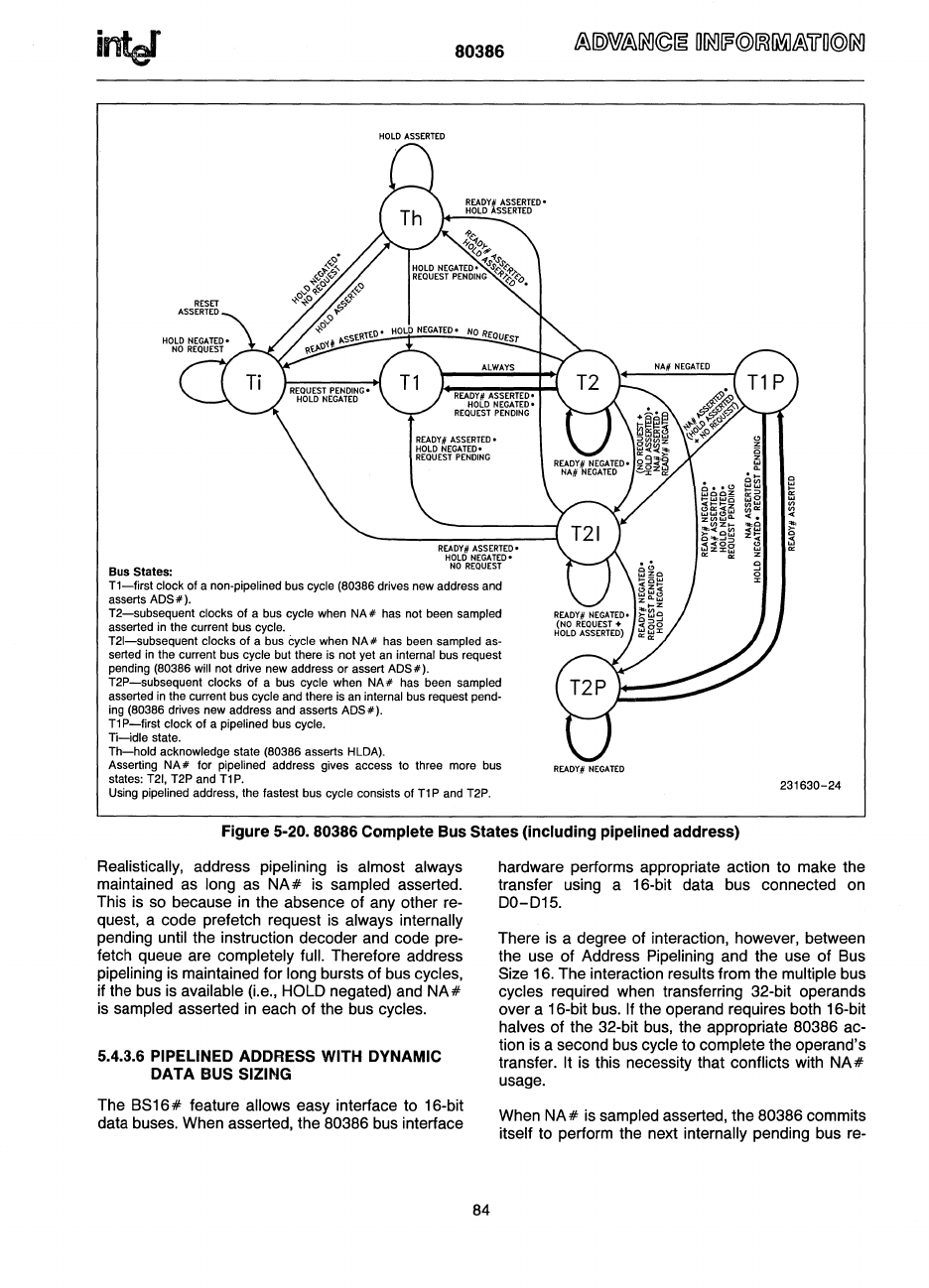

Bus States:

RESET

ASSERTED

80386

HOLD

ASSERTED

READY#

ASSERTED-

HOLD

NEGATED-

NO

REQUEST

T1-first

clock of a non·pipelined bus cycle (80386 drives new address and

asserts

ADS

#).

T2-subsequent

clocks of a bus cycle when

NA

#

has

not been sampled

asserted

in

the current bus cycle.

T21-subsequent clocks of a bus cycle when NA # has

been

sampled as·

serted

in

the current bus cycle but there

is

not yet

an

internal

bus

request

pending (80386

will not drive new address or assert ADS#).

T2P-subsequent clocks of a bus cycle when NA # has been sampled

asserted

in

the current bus cycle

and

there

is

an

internal

bus

request pend·

ing

(80386 drives new address and asserts ADS#).

T1

P-first

clock of a pipelined

bus

cycle.

Ti-idle

state.

Th-hold

acknowledge state (80386 asserts

HLDA).

Asserting NA # for pipelined address gives access to three more

bus

states:

T21,

T2P and

T1

P.

Using

pipe lined address, the fastest bus cycle consists of

T1

P

and

T2P.

READY#

NEGATED

Figure 5-20. 80386 Complete Bus States (including pipelined address)

"

z

"

~

.

~

"

,,~

~~

ffi

~8

~~

~

<.

~"

~

<~

z!<

~

9

'E

231630-24

Realistically, address pipelining is almost always

maintained

as

long as

NA#

is sampled asserted.

This is so because

in

the absence of any other re-

quest, a code prefetch request is always internally

pending

until the instruction decoder and code pre-

fetch queue are completely full. Therefore address

pipelining is maintained for long bursts of bus cycles,

if the bus is available (i.e.,

HOLD negated) and

NA#

is sampled asserted

in

each

of

the bus cycles.

hardware performs appropriate action to make the

transfer using a 16-bit data bus connected on

00-015.

5.4.3.6 PIPElINED ADDRESS WITH DYNAMIC

DATA

BUS SIZING

The BS 16 # feature allows easy interface to 16-bit

data buses. When asserted, the

80386 bus interface

84

There is a degree of interaction, however, between

the use of Address Pipelining and the use

of

Bus

Size 16. The interaction results from the multiple bus

cycles required when transferring 32-bit operands

over a 16-bit bus.

If the operand requires both 16-bit

halves

of

the 32-bit bus, the appropriate 80386 ac-

tion is a second bus cycle to complete the operand's

transfer.

It is this necessity that conflicts with

NA#

usage.

When

NA#

is sampled asserted, the 80386 commits

itself to perform the next internally pending bus re-