inter

80386

5.8

COPROCESSOR INTERFACING

The 80386 provides an automatic interface for the

Intel 80287 or 80387 numeric floating-point coproc-

essors. The

80287 and 80387 coprocessors use

an

I/O-mapped interface driven automatically

by

the

80386 and assisted

by

three dedicated signals:

BUSY

#,

ERROR

#,

and PEREa.

As the

80386 begins supporting a coprocessor in-

struction, it tests the BUSY # and ERROR # signals

to determine if the coprocessor can accept its next

instruction. Thus, the

BUSY # and ERROR # inputs

eliminate the need for any

"preamble" bus cycles

for communication between processor and coproc-

essor. The

80287 and 80387 can

be

given its com-

mand opcode immediately. The dedicated signals

provide instruction synchronization, and eliminate

the need of using the

80386 WAIT opcode (9Bh) for

80287/80387 instruction synchronization (the WAIT

opcode was required when 8086

or

8088 was used

with the

8087 coprocessor).

Custom coprocessors can be included

in

80386-

based systems, via memory-mapped or I/O-mapped

interfaces. Such coprocessor interfaces allow a

completely custom protocol, and are not limited to a

set of coprocessor protocol

"primitives". Instead,

memory-mapped or I/O-mapped interfaces may use

all applicable 80386 instructions for high-speed co-

processor communication. The BUSY # and

ERROR # inputs of the 80386 may also be used for

the custom coprocessor interface, if such hardware

assist

is

desired. These signals can be tested

by

the

80386 WAIT opcode (9Bh). The WAIT instruction

will wait until the BUSY # input

is

negated (interrupt-

able

by

an

NMI

or enabled INTR input), but gener-

ates

an

exception 16 fault if the ERROR #

pin

is

in

the asserted state when the BUSY # goes (or

is)

negated. If the custom coprocessor interface

is

memory-mapped, protection of the addresses used

for the interface can

be

provided with the 80386 on-

chip paging or segmentation mechanisms.

If

the

custom interface is

I/O-mapped, protection of the

interface can be provided with the

80386

10PL

(I/O

Privilege Level) mechanism.

The

80287 and 80387 numeric coprocessor interfac-

es are

I/O

mapped

as

shown

in

Table 5-11. Note

that the

80287/80387 coprocessor interface ad-

dresses are beyond the Oh-FFFFh range for pro-

grammed I/O. When the 80386 supports the 80287

or 80387 coprocessors, the 80386 automatically

generates bus cycles to the coprocessor interface

addresses.

93

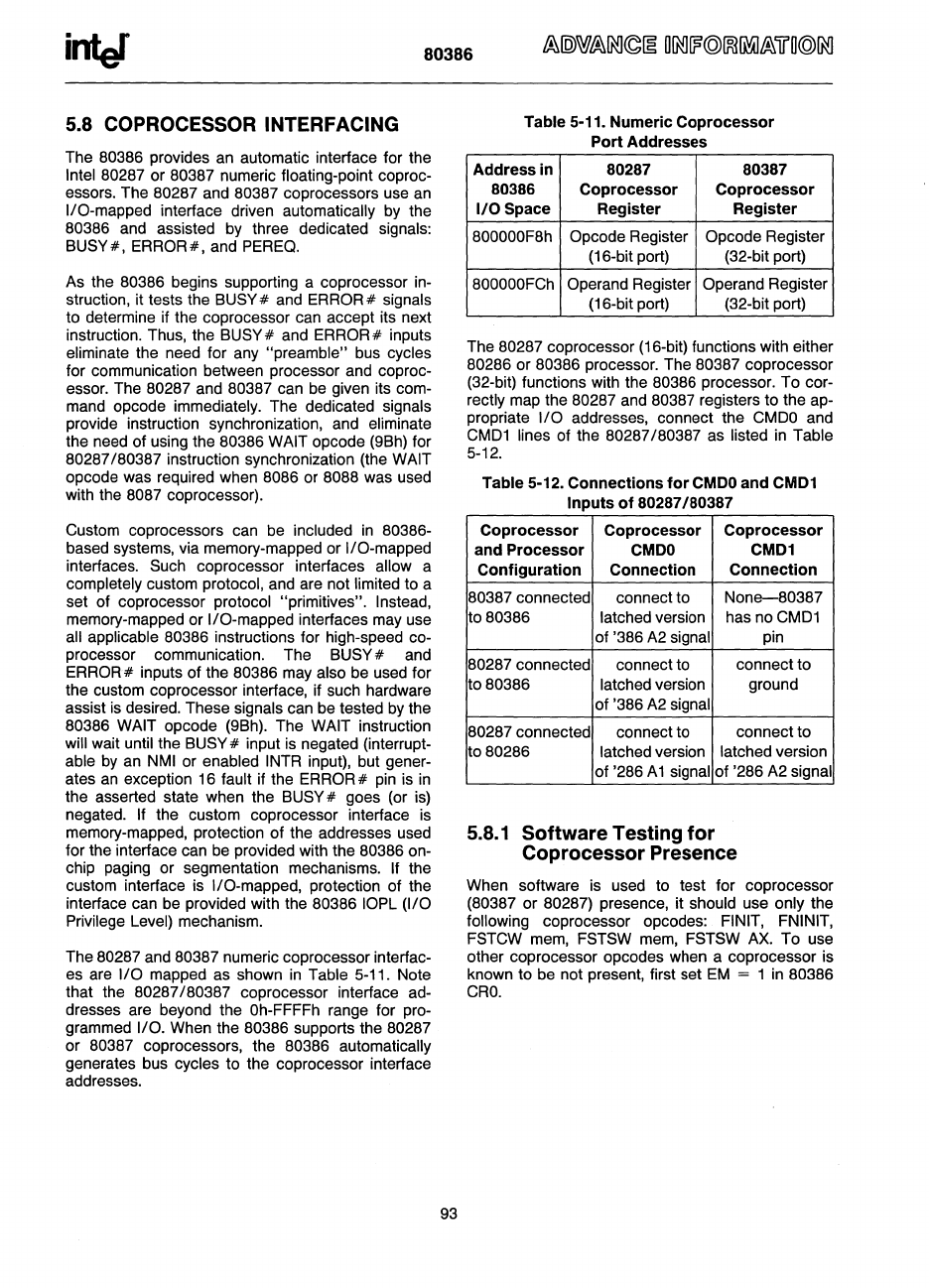

Table

5·11. Numeric

Coprocessor

Port

Addresses

Address

in 80287 80387

80386

Coprocessor

Coprocessor

I/O

Space Register Register

800000F8h Opcode Register Opcode Register

(16-bit port) (32-bit port)

800000FCh Operand Register

Operand Register

(16-bit port) (32-bit port)

The

80287 coprocessor (16-bit) functions with either

80286 or 80386 processor. The 80387 coprocessor

(32-bit) functions with the

80386 processor. To cor-

rectly map the 80287 and 80387 registers to the ap-

propriate

I/O

addresses, connect the

CMDO

and

CMD1

lines of the 80287/80387 as listed

in

Table

5-12.

Table

5·12.

Connections

for

CMDO

and CMD1

Inputs

of

80287180387

Coprocessor

Coprocessor

Coprocessor

and

Processor

CMDO

CMD1

Configuration

Connection

Connection

80387 connected connect to

None-80387

to 80386 latched version

has no

CMD1

of '386

A2

signal pin

80287 connected connect

to

connect to

to

80386

latched version

ground

of '386

A2

signal

80287 connected

connect

to

connect to

to

80286 latched version latched version

of '286 A 1 signal of '286

A2

signal

5.8.1

Software Testing

for

Coprocessor Presence

When software is used to test for coprocessor

(80387 or 80287) presence, it should use only the

following coprocessor opcodes:

FIN

IT,

FNINIT,

FSTCW

mem,

FSTSW

mem,

FSTSW

AX.

To use

other coprocessor opcodes when a coprocessor is

known to be not present, first set

EM

= 1

in

80386

CRO.