inter

IDLE

Ti

CLK2 [

-

M

(82384

CLK) [

-

V

80386

A

TRANSFER

REQUIRING

TWO

CYCLES

ON

16-81T

DATA

BUS

CYCLE

1

CYCLE

1 A

NON-PIPELINED NON-PIPELINED

(READ

----!---READ)

PART

ONE

PART

TWO

T1

T2

T

2

T

I

T2 T2

nIL

M

rm

rtJl

nIL

nIL

V

V V

V

V

V

CYCLE

2

NON-PIPELINED

(WRITE)

T1

T2

T2

nIL

rtJl

nIL

V

V

V

8EO

#.

8El

#

[

[

XIXXXXX

VALID I

I

NEGATED

DURING

i\

VALID 2

PART

TWO

8E2

#.

8E3 #

A2-

A31.

M/IO#.

D/C#

W/R#

[

ADS#

[

J.lXX.X)

X

~

~

LV

I

VALID I VALID 2

/

"---

I

"---

V

N TE: NA#

MUST

BE

NEGATED

HERE

TO

ALLOW

RECOGNITION

OF

ASSERTED

BSI6#

IN

FINAL T2

NA#

[

XIXXXX

,XXXXY

'<

X~~~~

DOO()(¥

'X

~~~~~{

XXXX

rY

'(

XXX

~

BUS

~ZE

BSI6#

[

)[XXX

:XX'x

XXX X

)..

"

IXXXX

wOO<

~

J,

XXX XXX

'1/

'\

16-BIT

16-81T

BUS

SIZE

BUS

SIZE

READY

#

[

) XXX)

DOOC

<XI

~

I

IX)

'XY

~I

IX

'XI

~

LOCK#

[

)(

Y.'J.'X'J.

~

VALID I VALID 2

dO-dl5

d16-d31

dO-dl5

DO-

D15

[

- ----

----

---

--0--

---

--0<

OUT

IGNORED

IGNORED

d16-d31

D16-

D31

[

- ----

----

--

_.

--0--

---

--0

OUT

Key:

On

= physical data pin n

dn

= logical data bit n

I I

I

231630-19

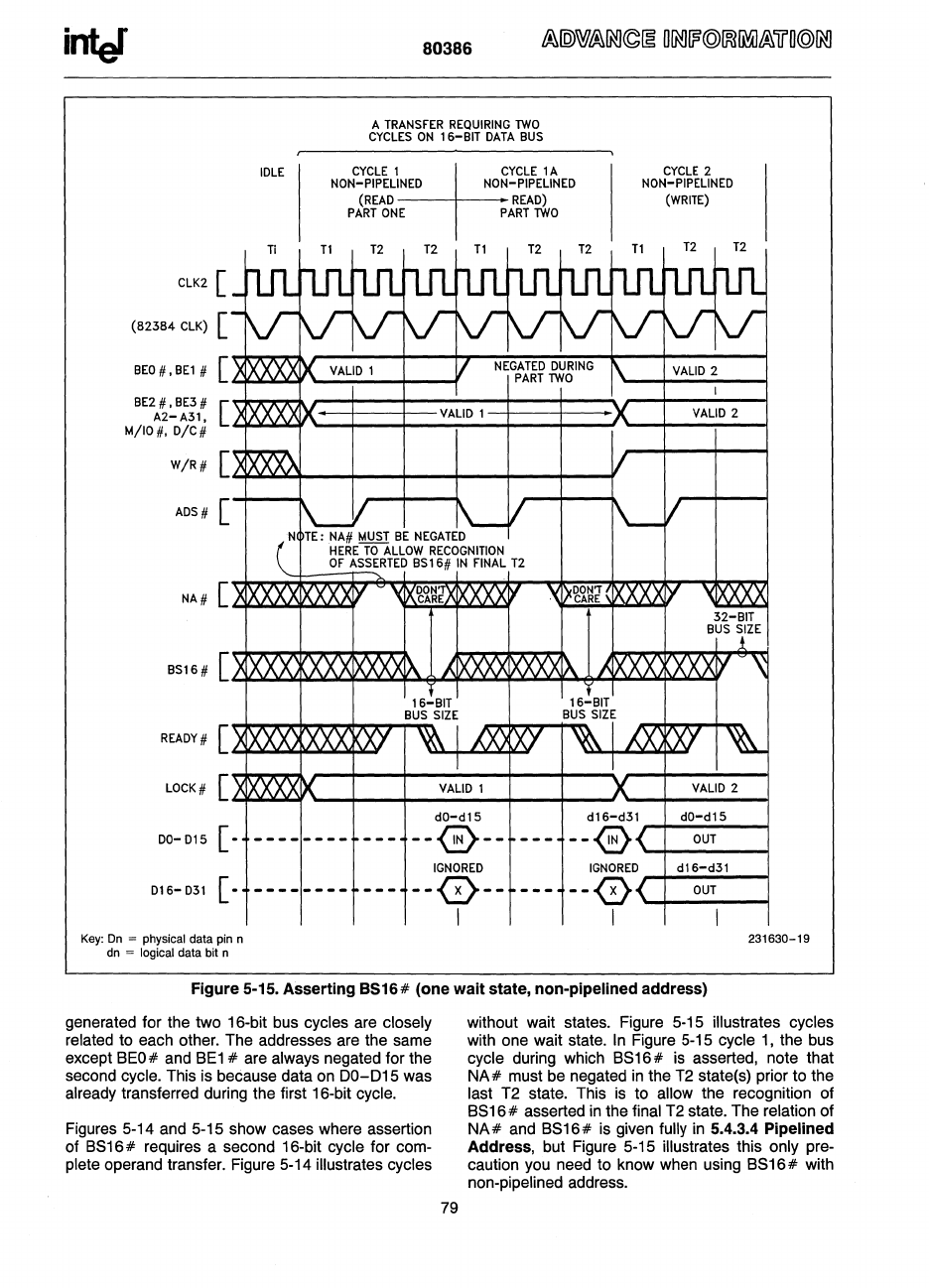

Figure 5-15. Asserting

8S16#

(one

wait

state, non-pipelined address)

generated for the two 16-bit bus

cycles

are

closely

related

to each other. The addresses are the same

except 8EO#

and

8E1

# are always negated for the

second

cycle. This is because data

on

DO-D15 was

already transferred during the first 16-bit cycle.

Figures 5-14

and

5-15 show cases where assertion

of

8816#

requires a second 16-bit cycle for com-

plete

operand transfer. Figure

5-14

illustrates cycles

79

without wait states. Figure

5-15

illustrates cycles

with one wait state.

In

Figure

5-15

cycle

1,

the bus

cycle during which

8816#

is

asserted, note that

NA#

must

be

negated

in

the

T2

state(s) prior to the

last

T2

state. This

is

to allow the recognition of

8816#

asserted

in

the final

T2

state. The relation of

NA#

and

8816#

is given fully

in

5.4.3.4 Pipelined

Address, but Figure

5-15

illustrates this only pre-

caution you

need

to know

when

using

8816#

with

non-pipelined address.