80386

the processor

to

execute the interrupt service rou-

tine pointed to

by

the nth vector

in

the interrupt ta-

ble.

A special case of the two byte software interrupt

INT

n is the one byte INT

3,

or breakpoint interrupt. By

inserting this one byte instruction

in

a program, the

user can set breakpoints

in

his program as a debug-

ging

tool.

A final type of software interrupt, is the single step

interrupt. It

is

discussed

in

section 2.12.

2.9.6 Interrupt and Exception

Priorities

Interrupts are externally-generated events. Maska-

ble

Interrupts (on the INTR input) and Non-Maskable

Interrupts (on the NMI input) are recognized at in-

struction boundaries. When NMI and maskable

INTR are

both

recognized at the

same

instruction

boundary, the 80386 invokes the

NMI service rou-

tine first.

If,

after the NMI service routine has been

invoked, maskable interrupts are

still enabled, then

the 80386 will invoke the appropriate interrupt serv-

ice routine.

Table

2·6a. 80386

Priority

for

Invoking

Service

Routines

in

Case

of

Simultaneous

El(ternal

Interrupts

1.

NMI

2.INTR

Exceptions are internally-generated events. Excep-

tions are detected by the 80386

if,

in

the course of

executing

an

instruction, the 80386 detects a prob-

lematic condition. The 80386 then immediately in-

vokes the appropriate exception service routine. The

state of the 80386 is such that the instruction caus-

ing the exception can be restarted.

If the exception

service routine has taken care of the problematic

condition, the instruction

will execute without caus-

ing the same exception.

It is possible for a single instruction to generate sev-

eral exceptions (for example, transferring a single

operand could generate two page faults if the oper-

and location spans two

"not

present" pages). How-

ever, only one exception

is

generated upon each at-

tempt to execute the instruction. Each exception

service routine should correct its corresponding ex-

ception, and restart the instruction.

In

this manner,

exceptions are serviced until the instruction exe-

cutes successfully.

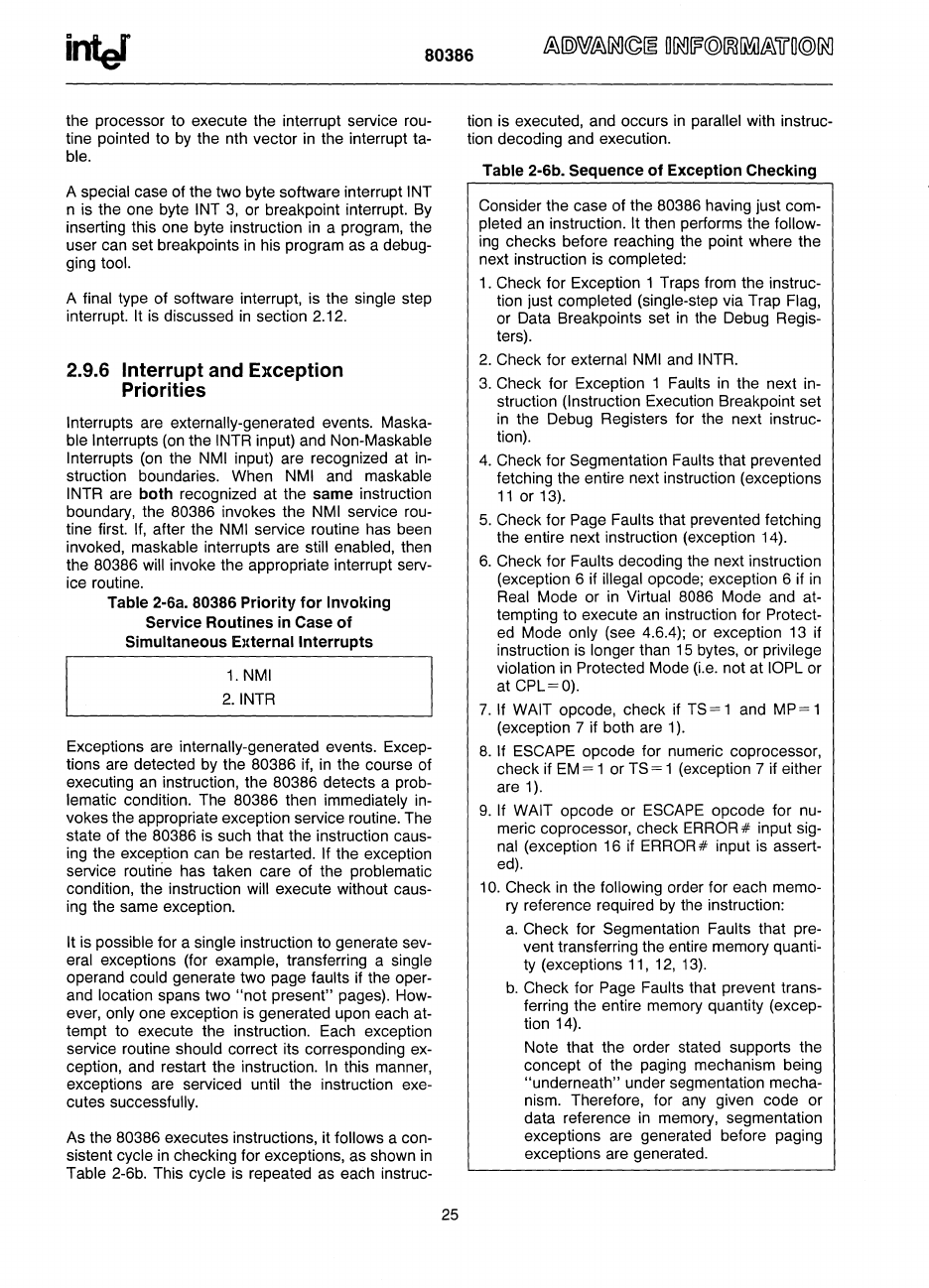

As the 80386 executes instructions, it

follows a con-

sistent cycle

in

checking for exceptions, as shown

in

Table 2-6b. This cycle

is

repeated as each instruc-

25

tion is executed, and occurs

in

parallel with instruc-

tion decoding and execution.

Table

2-6b.

Sequence

of

Exception

Checking

Consider the case of the 80386 having just com-

pleted an instruction.

It then performs the follow-

ing checks before reaching the point where the

next instruction is completed:

1.

Check for Exception 1 Traps from the instruc-

tion just completed (single-step via Trap Flag,

or Data Breakpoints set

in

the Debug Regis-

ters).

2.

Check for external NMI and INTR.

3.

Check for Exception 1 Faults

in

the next in-

struction (Instruction Execution Breakpoint set

in

the Debug Registers for the next instruc-

tion).

4.

Check for Segmentation Faults that prevented

fetching the entire next instruction (exceptions

11

or 13).

5.

Check for Page Faults that prevented fetching

the entire next instruction (exception 14).

6.

Check for Faults decoding the next instruction

(exception 6 if

illegal opcode; exception 6 if

in

Real Mode or

in

Virtual 8086 Mode and at-

tempting to execute

an

instruction for Protect-

ed

Mode only (see 4.6.4); or exception 13 if

instruction is longer than

15

bytes, or privilege

violation in Protected Mode

(Le.

not at IOPL or

at CPL=O).

7. If WAIT opcode, check if

TS=1

and

MP=1

(exception 7 if both are 1).

B.

If ESCAPE opcode for numeric coprocessor,

check if

EM

= 1 or TS = 1 (exception 7 if either

are 1).

9. If WAIT opcode or ESCAPE opcode for nu-

meric coprocessor, check ERROR # input sig-

nal (exception 16 if

ERROR # input is assert-

ed).

10. Check

in

the following order for each memo-

ry reference required

by

the instruction:

a.

Check for Segmentation Faults that pre-

vent transferring the entire memory quanti-

ty (exceptions 11, 12, 13).

b.

Check for Page Faults that prevent trans-

ferring the entire memory quantity (excep-

tion 14).

Note that the order stated supports the

concept of the paging mechanism being

"underneath" under segmentation mecha-

nism. Therefore, for any given code or

data reference

in

memory, segmentation

exceptions are generated before paging

exceptions are generated.