HARDWARE IMPLEMENTATION

and device drivers, the effective width of the data

bus can be dynamically switched between

16

and

32

bits. This topic

is

discussed

in

a subsequent

section.

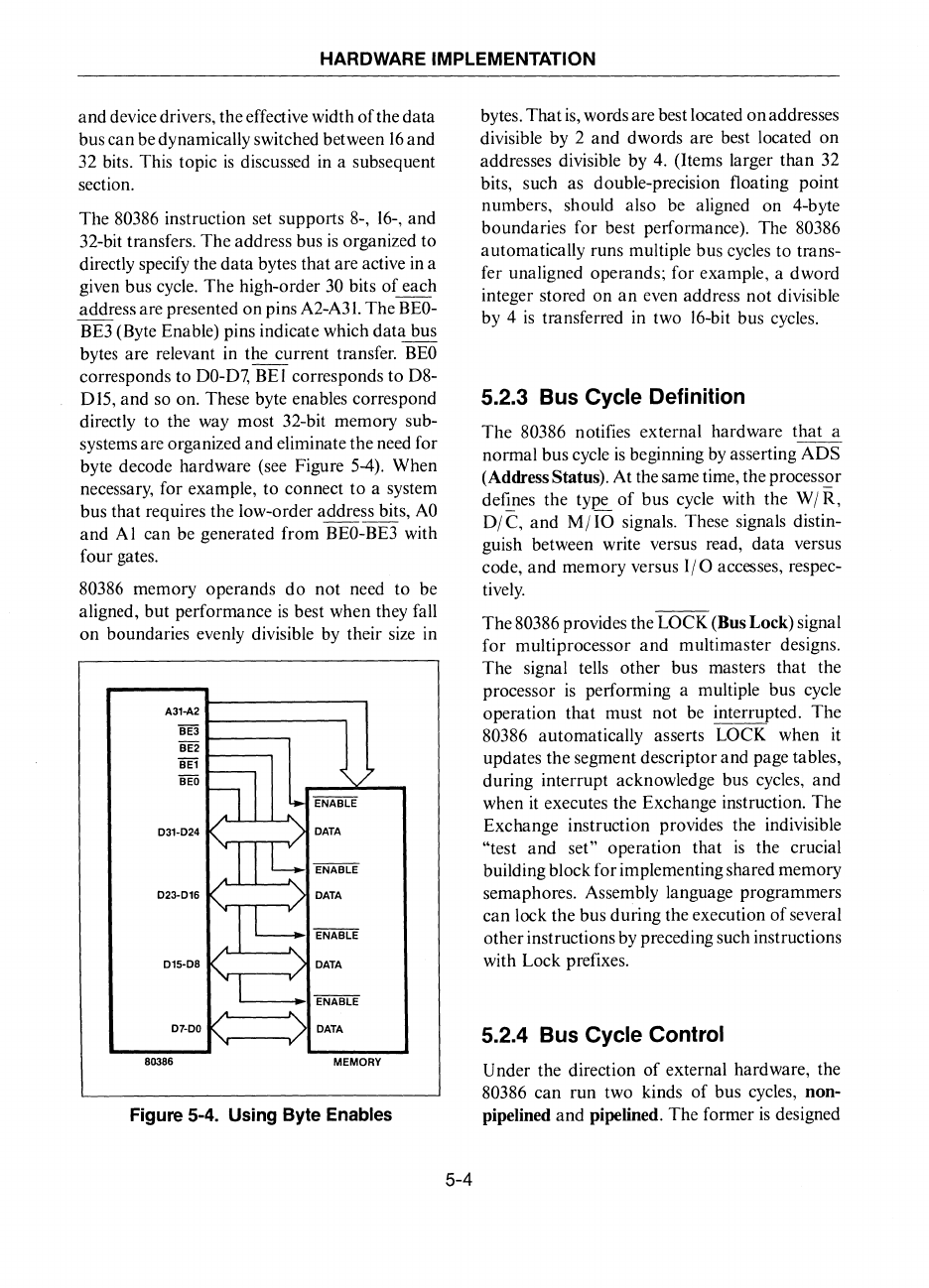

The

80386 instruction set supports

8-,

16-,

and

32-bit transfers. The address bus

is

organized to

directly specify the data bytes that are active

in

a

given bus cycle. The high-order

30

bits

of

each

address are presented on pins

A2-A31.

The

BEO-

BE3 (Byte Enable) pins indicate which data bus

bytes are relevant in the current transfer.

BEO

corresponds to

DO-D7,

BEl corresponds to D8-

DIS, and so on. These byte enables correspond

directly to the way most 32-bit memory sub-

systems are organized and eliminate the need for

byte decode hardware (see Figure

5-4).

When

necessary, for example, to connect to a system

bus that requires the low-order address bits,

AO

and AI can be generated from BEO-BE3 with

four gates.

80386 memory operands do not need to be

aligned, but performance

is

best when they fall

on boundaries evenly divisible

by

their size in

A31-A2

BE3

t----------.

BE2

BEl

t-------.

BED

031-024

023-016

015-08

07-00

80386

MEMORY

Figure 5-4. Using Byte Enables

5-4

bytes. That

is,

words are best located on addresses

divisible by 2 and dwords are best located on

addresses divisible by

4.

(Items larger than

32

bits, such as double-precision floating point

numbers, should also be aligned on 4-byte

boundaries for best performance). The

80386

automatically runs mUltiple bus cycles to trans-

fer unaligned operands; for example, a dword

integer stored on

an

even address not divisible

by 4

is

transferred in two

16-bit

bus cycles.

5.2.3 Bus Cycle Definition

The 80386 notifies external hardware that a

normal bus cycle

is

beginning

by

asserting

ADS

(Address Status). At the same time, the

process~r

defines the type

of

bus cycle with the

WI

R,

DI

C,

and

MI

10 signals. These signals distin-

guish between write versus read, data versus

code, and memory versus

110 accesses, respec-

tively.

The 80386 provides the LOCK (Bus Lock) signal

for multiprocessor and multimaster designs.

The signal tells other bus masters that the

processor

is

performing a multiple bus cycle

operation that must not

be

interrupted. The

80386 automatically asserts LOCK when

it

updates the segment descriptor and page tables,

during interrupt acknowledge bus cycles, and

when

it

executes the Exchange instruction. The

Exchange instruction provides the indivisible

"test and set" operation that

is

the crucial

building block for implementing shared memory

semaphores. Assembly language programmers

can lock the bus during the execution of several

other instructions by preceding such instructions

with Lock prefixes.

5.2.4 Bus Cycle Control

Under the direction

of

external hardware, the

80386 can run two kinds

of

bus cycles,

000-

pipelioed and pipelioed. The former

is

designed