80386

5.5 OTHER FUNCTIONAL

DESCRIPTIONS

5.5.1

Entering and Exiting Hold

Acknowledge

The bus hold acknowledge state,

Th,

is

entered

in

response to the HOLD input being asserted.

In

the

bus hold acknowledge state, the

80386 floats all

output or bidirectional signals, except for HLDA.

HLDA

is

asserted as long as the 80386 remains

in

the bus hold acknowledge state.

In

the bus hold ac-

knowledge state, all inputs except HOLD and

RE-

SET are ignored (also

up

to one rising edge

on

NMI

is

remembered for processing when HOLD

is

no

longer asserted).

r

ACK~g~~EDGE~

10LE

n

Th Th Th

n

10LE

(82384

CLK>[

8EO#-8E3# [

A2-A31.

M/IO#

L~~~

o/c#.

w/R#

-

AOS#[

LOCK#[

~~:.cJ(

----

(FLOATING)·---

I

(FLOATING)

---------------~----

00-031[.

231630-29

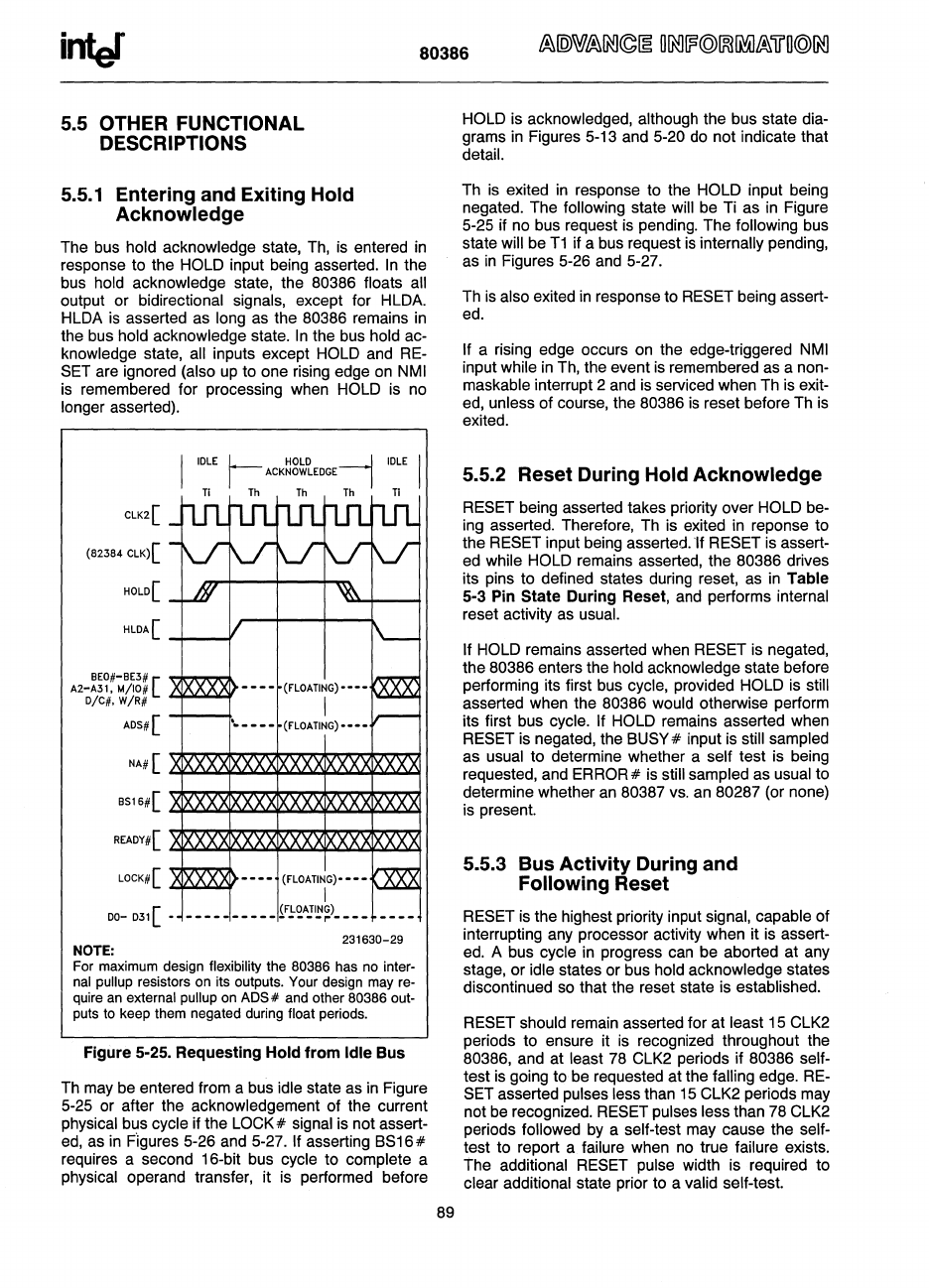

NOTE:

For maximum design flexibility the 80386 has no inter-

nal pullup

resistors on its outputs. Your design may re-

quire an external

PUIIUP

on ADS # and other 80386 out-

puts to keep them negated during float periods.

Figure 5-25. Requesting Hold from Idle Bus

Th

may

be entered from a bus idle state as

in

Figure

5-25 or after the acknowledgement of the current

physical bus cycle if the

LOCK# signal is not assert-

ed,

as

in

Figures 5-26 and 5-27. If asserting BS16#

requires a second 16-bit bus cycle to complete a

physical operand transfer, it is performed before

89

HOLD

is

acknowledged, although the bus state dia-

grams

in

Figures 5-13 and 5-20

do

not indicate that

detail.

Th

is

exited

in

response to the HOLD input being

negated. The

following state will be Ti as

in

Figure

5-25 if no bus request

is

pending. The following bus

state will

be

T1

if a bus request

is

internally pending,

as

in

Figures 5-26 and 5-27.

Th

is

also exited

in

response to RESET being assert-

ed.

If a rising edge occurs on the edge-triggered

NMI

input while

in

Th, the event

is

remembered as a non-

maskable interrupt 2 and

is

serviced when Th is exit-

ed, unless of course, the 80386

is

reset before Th

is

exited.

5.5.2 Reset During Hold Acknowledge

RESET being asserted takes priority over HOLD be-

ing asserted. Therefore, Th is exited

in

reponse to

the

RESET input being asserted. If RESET

is

assert-

ed while HOLD remains asserted, the 80386 drives

its pins to defined states during reset,

as

in

Table

5-3 Pin State During Reset, and performs internal

reset activity as

usual.

If HOLD

remains asserted when RESET

is

negated,

the

80386 enters the hold acknowledge state before

performing its first bus cycle, provided

HOLD is still

asserted when the

80386 would otherwise perform

its first bus cycle.

If HOLD remains asserted when

RESET is negated, the BUSY # input

is

still sampled

as usual to determine whether a self test

is

being

requested, and ERROR#

is

still sampled as usual to

determine whether

an

80387

vs.

an 80287 (or none)

is

present.

5.5.3

Bus

Activity During and

Following Reset

RESET

is

the highest priority input signal, capable of

interrupting any processor activity when it

is

assert-

ed.

A bus cycle

in

progress

can

be aborted at any

stage, or idle states or bus hold acknowledge states

discontinued

so

that the reset state is established.

RESET

should remain asserted for at least 15 CLK2

periods to ensure it

is

recognized throughout the

80386, and at least

78

CLK2 periods if 80386 self-

test

is

going to be requested at the falling edge.

RE-

SET asserted pulses less than

15

CLK2 periods may

not

be

recognized. RESET pulses less than 78 CLK2

periods

followed

by

a self-test may cause the self-

test to report a failure when

no

true failure exists.

The additional

RESET pulse width is required to

clear additional state prior to a

valid self-test.