SYSTEM

ARCHITECTURE

program

is

a text that describes

an

algorithm,

and a task

is

one execution (performance)

ofthat

algorithm.

The programs that tasks execute are designed as

though they were to run

on

dedicated processors

sharing a common memory; that

is,

except

ror

occasional pauses to communicate or synchronize

with other tasks, a task theoretically runs con-

tinuously in parallel with all other tasks. In fact,

however, the tasks run one at a time in short

bursts on a single processor.

The multitasking operating system simulates

mUltiple processors by providing each task with

a

"virtual processor." At any instant, the operating

system assigns the real processor to one of the

virtual processors, thereby running the associated

task.

To

maintain the illusion of one processor

per task, the operating system frequently switches

the

real processor to a different virtual proces-

sor. The

80386 system architecture supports this

critical task switch operation with

Task

State

Segments and instructions that switch tasks.

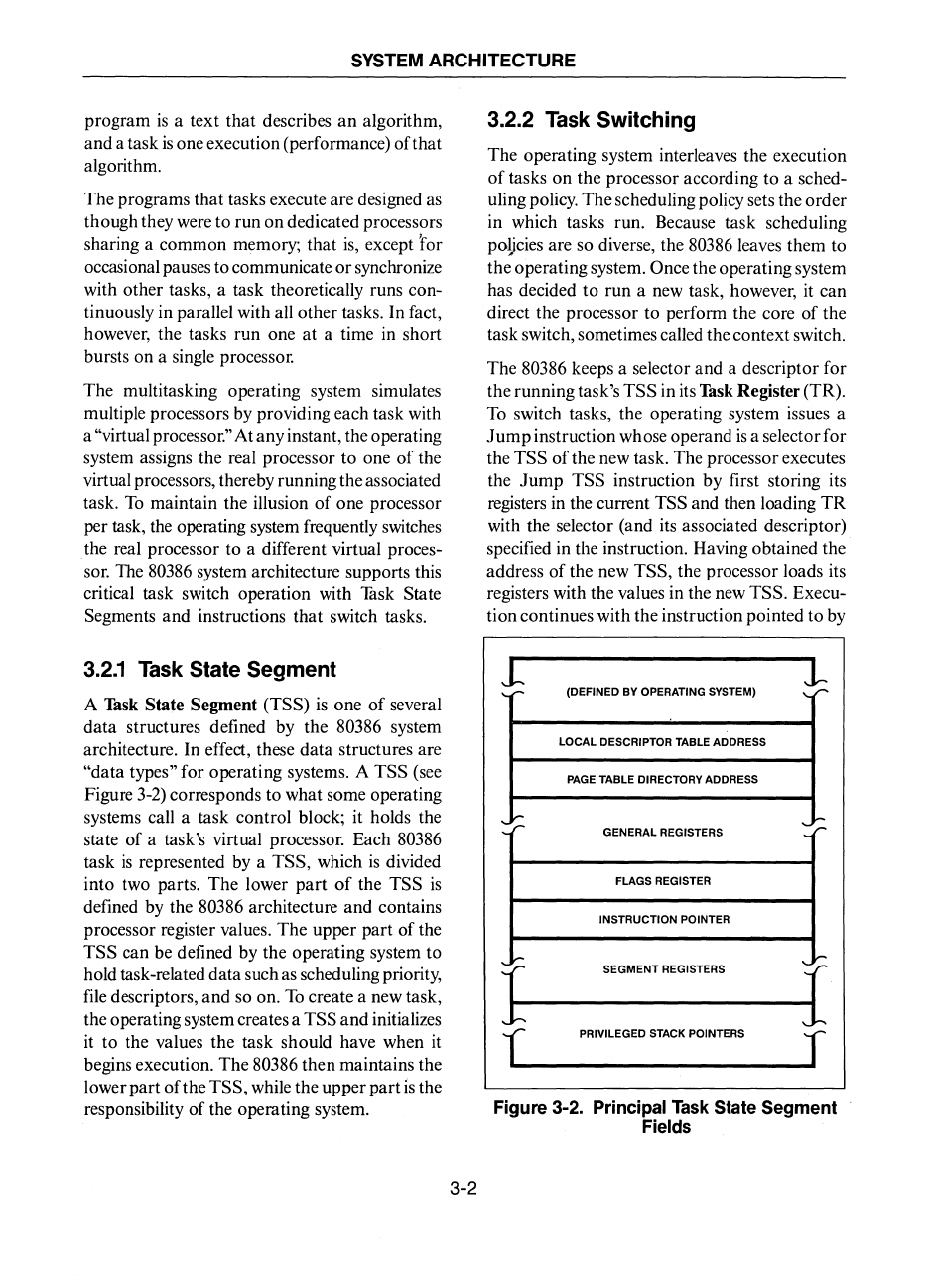

3.2.1

Task State Segment

A Task State Segment (TSS)

is

one

of

several

data structures defined by the

80386 system

architecture. In effect, these data structures are

"data types" for operating systems. A TSS (see

Figure

3-2)

corresponds to what some operating

systems call a task control block; it holds the

state

of

a task's virtual processor. Each 80386

task

is

represented by a TSS, which

is

divided

into two parts. The lower

part

of

the TSS

is

defined by the 80386 architecture and contains

processor register values. The upper part of the

TSS can be defined by the operating system to

hold task-related data such

as

scheduling priority,

file descriptors, and so on.

To

create a new task,

the operating system creates a

TSS and initializes

it to the values the task should have when it

begins execution. The

80386 then maintains the

lower

part

of

the TSS, while the upper

part

is

the

responsibility of the operating system.

3-2

3.2.2 Task Switching

The operating system interleaves the execution

of

tasks on the processor according to a sched-

uling policy.

The

scheduling policy sets the order

in which tasks run. Because task scheduling

poljcies are so diverse, the

80386 leaves them to

the operating system.

Once the operating system

has decided

to

run a new task, however, it can

direct the processor to perform the core of the

task switch, sometimes called the context switch.

The

80386 keeps a selector and a descriptor for

the running task's

TSS in its Task Register (TR).

To

switch tasks, the operating system issues a

Jump

instruction whose operand

is

a selector for

the

TSS

of

the new task. The processor executes

the

Jump

TSS instruction

by

first storing its

registers in the current

TSS and then loading

TR

with the selector (and its associated descriptor)

specified in the instruction. Having obtained the

address of the new

TSS, the processor loads its

registers with the values in the new

TSS. Execu-

tion continues with the instruction pointed to by

1

l-

..

--

(DEFINED

BY

OPERATING SYSTEM) ,roo

LOCAL

DESCRIPTOR TABLE ADDRESS

PAGE TABLE

DIRECTORY ADDRESS

..

~

GENERAL REGISTERS

~

~

FLAGS REGISTER

INSTRUCTION

POINTER

..

'"

....

--

SEGMENT

REGISTERS

I

PRIVILEGED STACK POINTERS

r

Figure 3-2. Principal

Task

State Segment

Fields