SYSTEM ARCHITECTURE

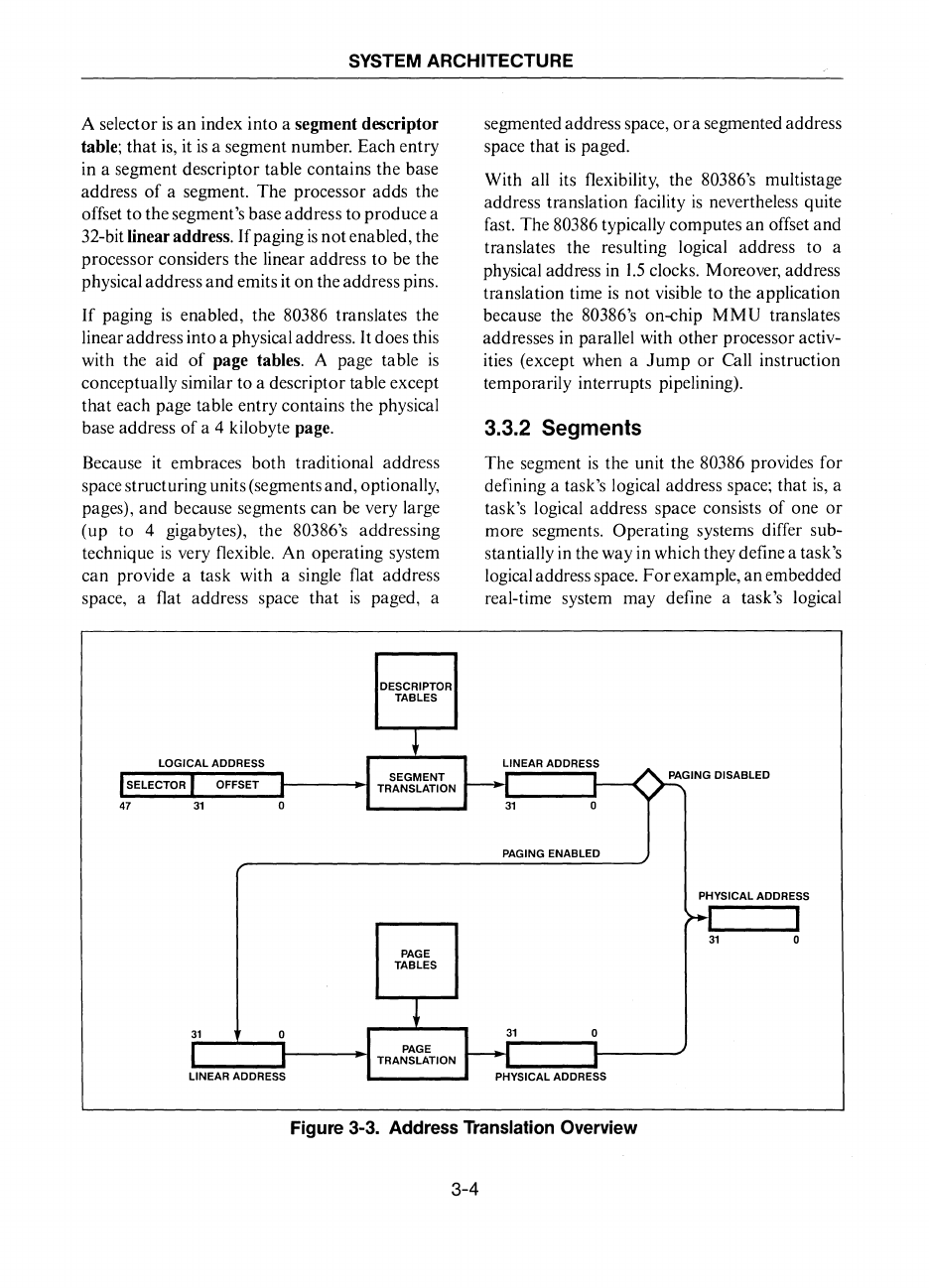

A selector

is

an

index into a segment descriptor

table; that

is,

it

is

a segment number. Each entry

in a segment descriptor table contains the base

address

of

a segment. The processor adds the

offset to the segment's base address to produce a

32-bit

linear address. If paging

is

not enabled, the

processor considers the linear address to be the

physical address and emits it on the address pins.

If paging

is

enabled, the 80386 translates the

linear address into a physical address.

It

does this

with the aid

of

page tables. A page table

is

conceptually similar to a descriptor table except

that each page table entry contains the physical

base address

of

a 4 kilobyte page.

Because it embraces both traditional address

space structuring units (segments and, optionally,

pages), and because segments can

be

very large

(up to 4 gigabytes), the 80386's addressing

technique

is

very flexible. An operating system

can provide a task with a single flat address

space, a flat address space that

is

paged, a

LOGICAL ADDRESS

OFFSET

31

LINEAR ADDRESS

DESCRIPTOR

TABLES

PAGE

TABLES

segmented address space,

or

a segmented address

space that

is

paged.

With all its flexibility, the

80386's multistage

address translation facility

is

nevertheless quite

fast. The

80386 typically computes an offset and

translates the resulting logical address to a

physical address

in

1.5

clocks. Moreover, address

translation time

is

not visible to the application

because the 80386's on-chip

MMU

translates

addresses

in

parallel with other processor activ-

ities (except when a

Jump

or

Call instruction

temporarily interrupts pipelining).

3.3.2 Segments

The segment

is

the unit the 80386 provides for

defining a task's logical address space; that

is,

a

task's logical address space consists of one

or

more segments. Operating systems differ sub-

stantially

in

the way in which they define a task's

logical address space.

For

example,

an

embedded

real-time system may define a task's logical

PAGING ENABLED

PHYSICAL ADDRESS

Figure 3-3.

Address

Translation

Overview

3-4