Timing Diagrams

280

NS7520 Hardware Reference, Rev. D 03/2006

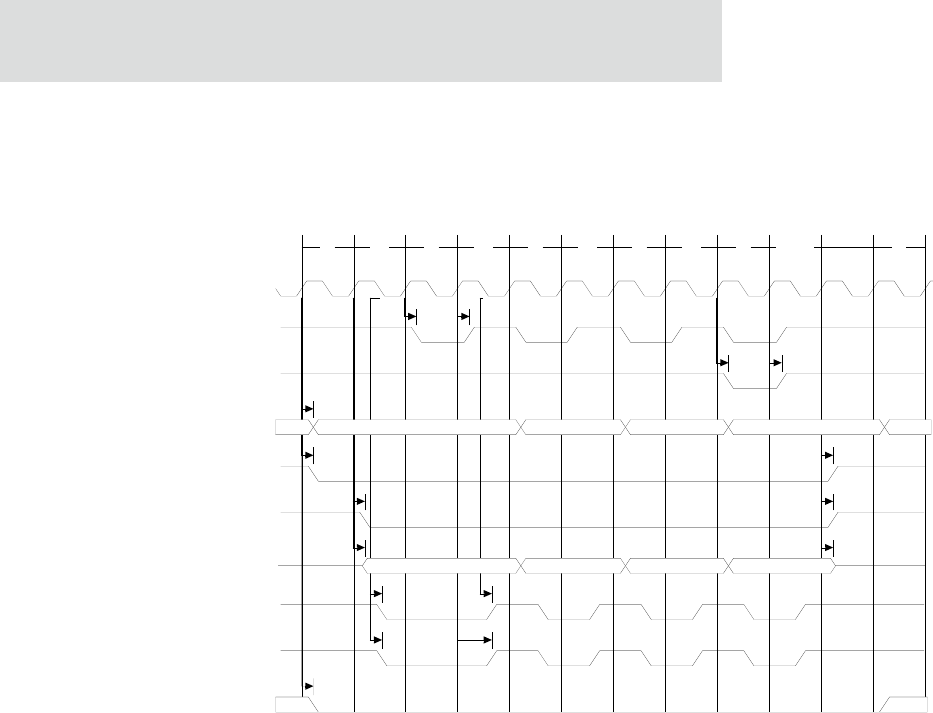

SRAM WE burst write

WE* controlled, four word (3-2-2-2), burst write (wait = 2, BCYC = 01)

Notes:

1 At least one null period occurs between memory transfers. More null periods can

occur if the next transfer is DMA. Thirteen clock pulses are required for DMA

context switching.

2 Port size determines which byte enable signals are active:

– 8-bit port = BE3*

– 16-bit port = BE[3:0]

– 32-bit port = BE[3:0]

3 The TW cycles are present when the WAIT field is set to 2 or more.

4 The TA* and TEA*/LAST signals are for reference only.

T1 TW T2 TW T2 TW T2 TW T2 Note-1 T1

12

1919

2929

139

2727

3636

6

3131

3030

Note-2

BCLK

TA* (Note-4)

TEA*/LAST (Note-4)

A[27:0]

BE[3:0]*

CS[4:0]*

write D[31:0]

Async WE*

CS0WE*

RW*