S3C2410A ARM INSTRUCTION SET

3-25

MULTIPLY LONG AND MULTIPLY-ACCUMULATE LONG (MULL, MLAL)

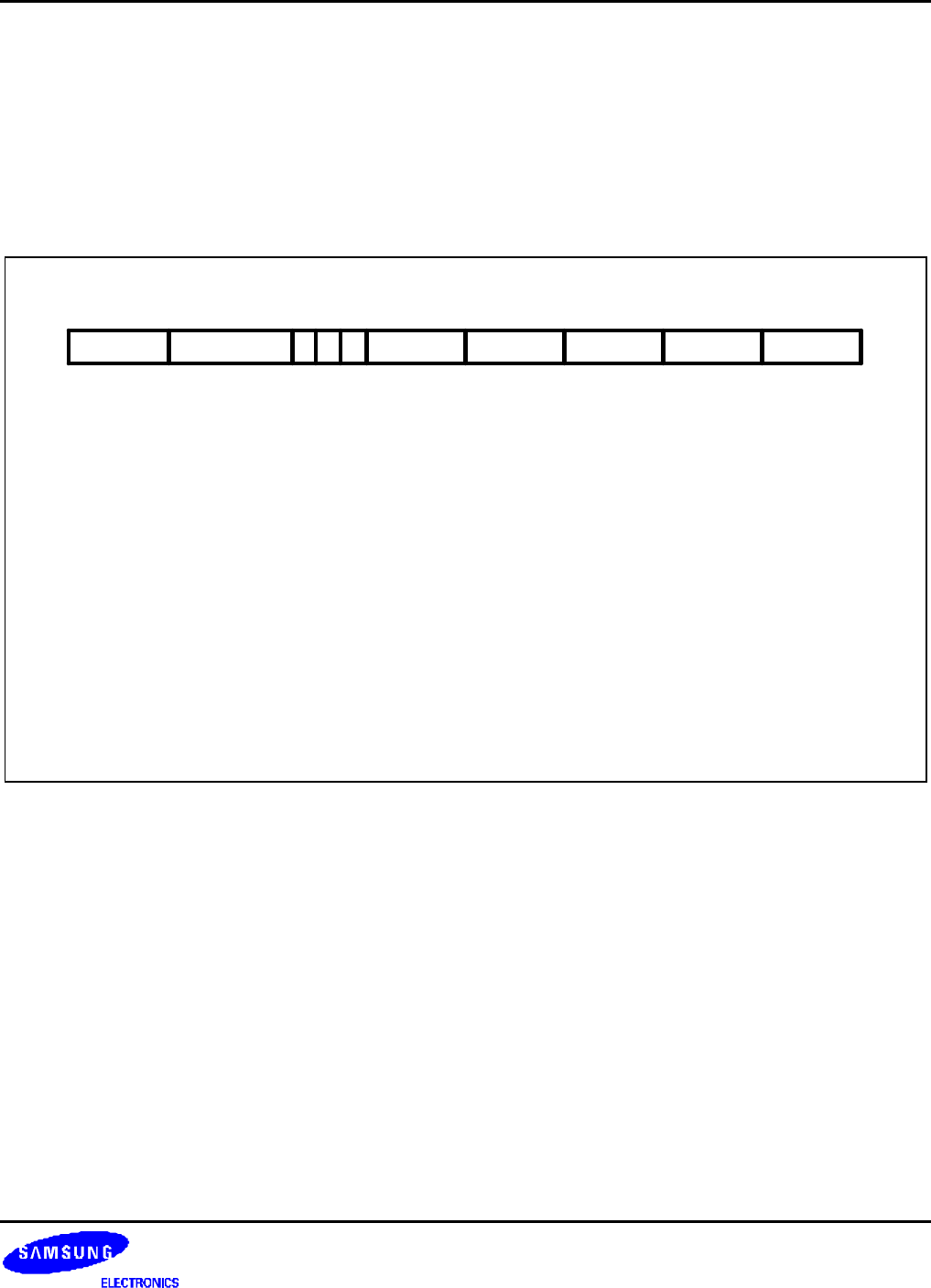

The instruction is only executed if the condition is true. The various conditions are defined in Table 3-2. The

instruction encoding is shown in Figure 3-13.

The multiply long instructions perform integer multiplication on two 32-bit operands and produce 64-bit results.

Signed and unsigned multiplication each with optional accumulate give rise to four variations.

31 27 19 15

Cond

28 16 11122123

U

20

S RdHi RdLo

[11:8][3:0] Operand Registers

[19:16][15:12] Source Destination Registers

[20] Set Condition Code

0 = Do not alter condition codes

1 = Set condition codes

[21] Accumulate

0 = Multiply only

1 = Multiply and accumulate

[22] Unsigned

0 = Unsigned

1 = Signed

[31:28] Condition Field

22

00 0 0 1 1 0 0 1Rs RmA

8 7 4 3 0

Figure 3-13. Multiply Long Instructions

The multiply forms (UMULL and SMULL) take two 32-bit numbers and multiply them to produce a 64-bit result of the

form RdHi,RdLo := Rm * Rs. The lower 32 bits of the 64-bit result are written to RdLo, the upper 32 bits of the result

are written to RdHi.

The multiply-accumulate forms (UMLAL and SMLAL) take two 32-bit numbers, multiply them and add a 64 bit

number to produce a 64-bit result of the form RdHi,RdLo := Rm * Rs + RdHi,RdLo. The lower 32 bits of the 64-bit

number to add is read from RdLo. The upper 32 bits of the 64 bit number to add is read from RdHi. The lower 32 bits

of the 64-bit result are written to RdLo. The upper 32 bits of the 64 bit result are written to RdHi.

The UMULL and UMLAL instructions treat all of their operands as unsigned binary numbers and write an unsigned 64

bit result. The SMULL and SMLAL instructions treat all of their operands as two's-complement signed numbers and

write a two's-complement signed 64-bit result.