S3C2410A IIC-BUS INTERFACE

20-5

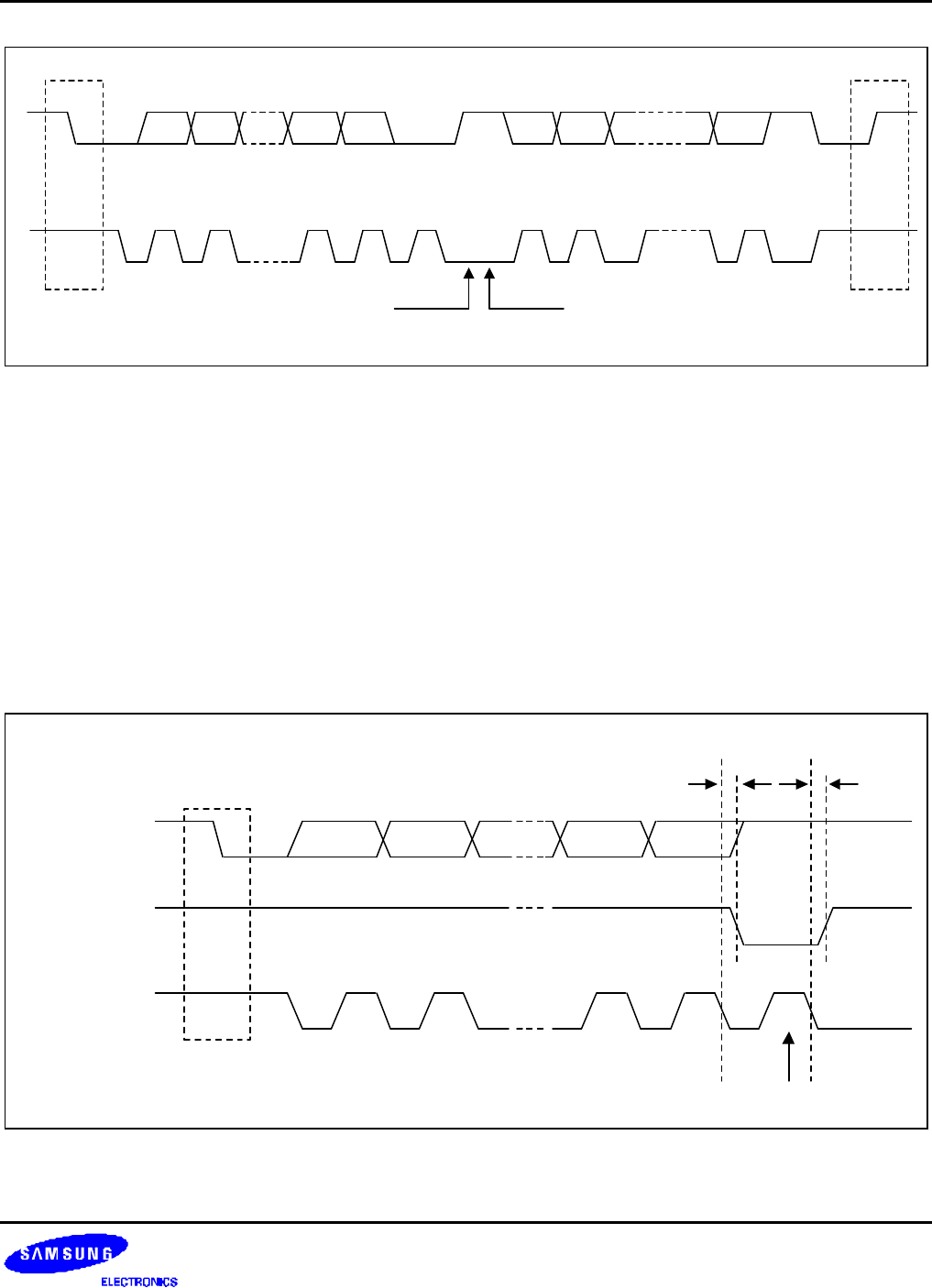

SDA

Acknowledgement

Signal from Receiver

SCL

S

1 2 7 8 9 1 2 9

Acknowledgement

Signal from Receiver

MSB

ACK

Byte Complete, Interrupt

within Receiver

Clock Line Held Low by

receiver and/or transmitter

Figure 20-4. Data Transfer on the IIC-Bus

ACK SIGNAL TRANSMISSION

To complete a one-byte transfer operation, the receiver should send an ACK bit to the transmitter. The ACK pulse

should occur at the ninth clock of the SCL line. Eight clocks are required for the one-byte data transfer. The master

should generate the clock pulse required to transmit the ACK bit.

The transmitter should release the SDA line by making the SDA line High when the ACK clock pulse is received. The

receiver should also drive the SDA line Low during the ACK clock pulse so that the SDA keeps Low during the High

period of the ninth SCL pulse.

The ACK bit transmit function can be enabled or disabled by software (IICSTAT). However, the ACK pulse on the

ninth clock of SCL is required to complete the one-byte data transfer operation.

Data Output by

Transmitter

Data Output by

Receiver

SCL from

Master

Start

Condition

Clock Pulse for Acknowledgment

Clock to Output

987

S

1 2

Figure 20-5. Acknowledge on the IIC-Bus