S3C2410A IIC-BUS INTERFACE

20-11

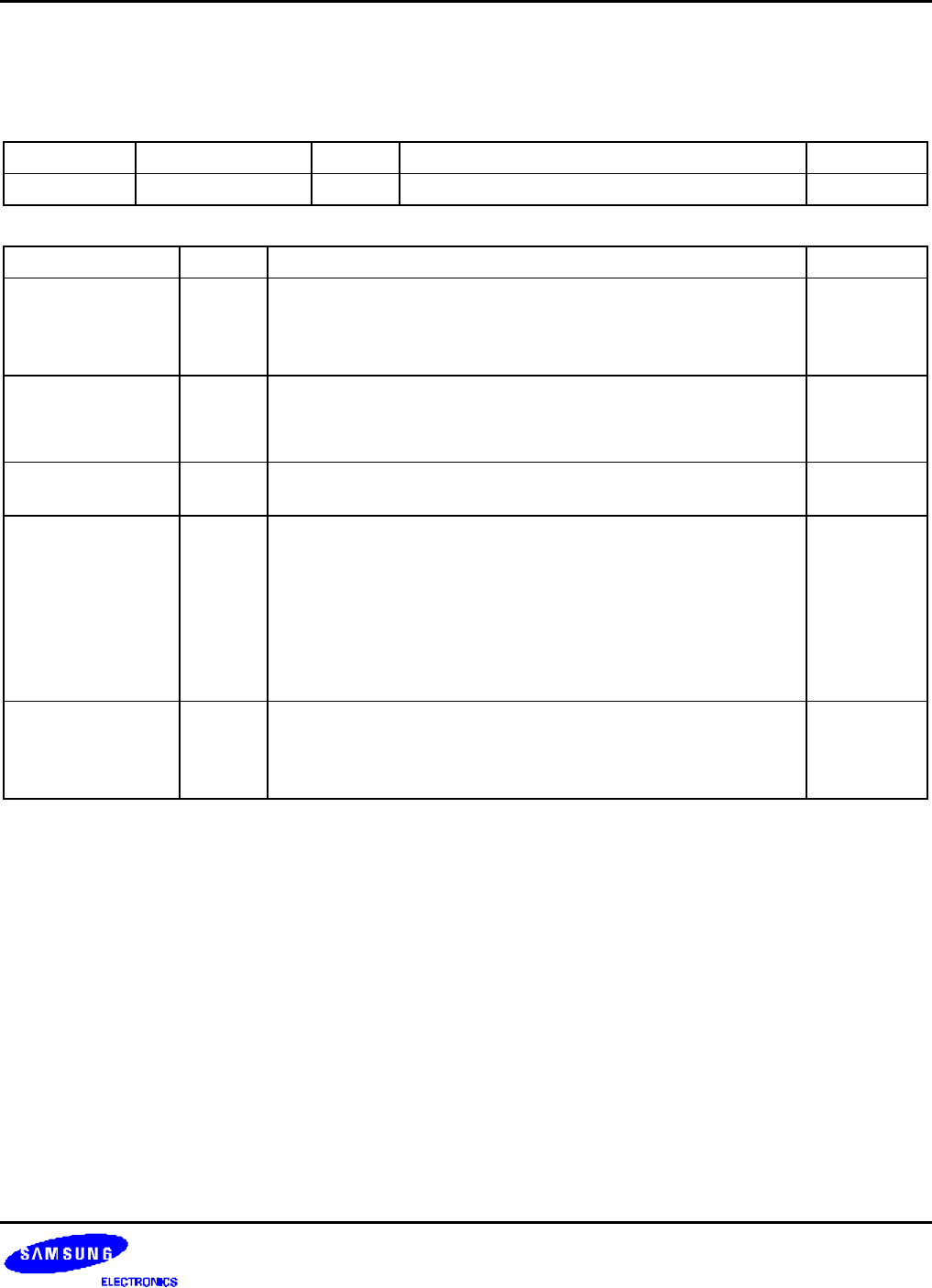

IIC-BUS INTERFACE SPECIAL REGISTERS

MULTI-MASTER IIC-BUS CONTROL (IICCON) REGISTER

Register Address R/W Description Reset Value

IICCON 0x54000000 R/W IIC-Bus control register 0x0X

IICCON Bit Description Initial State

Acknowledge

generation

(note 1)

[7] IIC-bus acknowledge enable bit.

0 = Disable, 1 = Enable

In Tx mode, the IICSDA is free in the ack time.

In Rx mode, the IICSDA is L in the ack time.

0

Tx clock source

selection

[6] Source clock of IIC-bus transmit clock prescaler selection bit.

0 = IICCLK = f

PCLK

/16

1 = IICCLK = f

PCLK

/512

0

Tx/Rx Interrupt

(note 5)

[5] IIC-Bus Tx/Rx interrupt enable/disable bit.

0 = Disable, 1 = Enable

0

Interrupt pending

flag

(note 2), (note 3)

[4] IIC-bus Tx/Rx interrupt pending flag. This bit cannot be written to

1. When this bit is read as 1, the IICSCL is tied to L and the IIC is

stopped. To resume the operation, clear this bit as 0.

0 = 1) No interrupt pending (when read).

2) Clear pending condition &

Resume the operation (when write).

1 = 1) Interrupt is pending (when read)

2) N/A (when write)

0

Transmit clock

value

(note 4)

[3:0] IIC-Bus transmit clock prescaler.

IIC-Bus transmit clock frequency is determined by this 4-bit

prescaler value, according to the following formula:

Tx clock = IICCLK/(IICCON[3:0]+1).

Undefined

NOTES:

1. Interfacing with EEPROM, the ack generation may be disabled before reading the last data in order to generate the

STOP condition in Rx mode.

2. An IIC-bus interrupt occurs 1) when a 1-byte transmit or receive operation is completed, 2) when a general call or a

slave address match occurs, or 3) if bus arbitration fails.

3. To adjust the setup time of IICSDA before IISSCL rising edge, IICDS has to be written before clearing the IIC interrupt

pending bit.

4. IICCLK is determined by IICCON[6].

Tx clock can vary by SCL transition time.

When IICCON[6]=0, IICCON[3:0]=0x0 or 0x1 is not available.

5. If the IICON[5]=0, IICON[4] does not operate correctly.

So, It is recommended that you should set IICCON[5]=1, although you does not use the IIC interrupt.