ARM920T PROCESSOR CLOCK MODES

5-3

ASYNCHRONOUS MODE

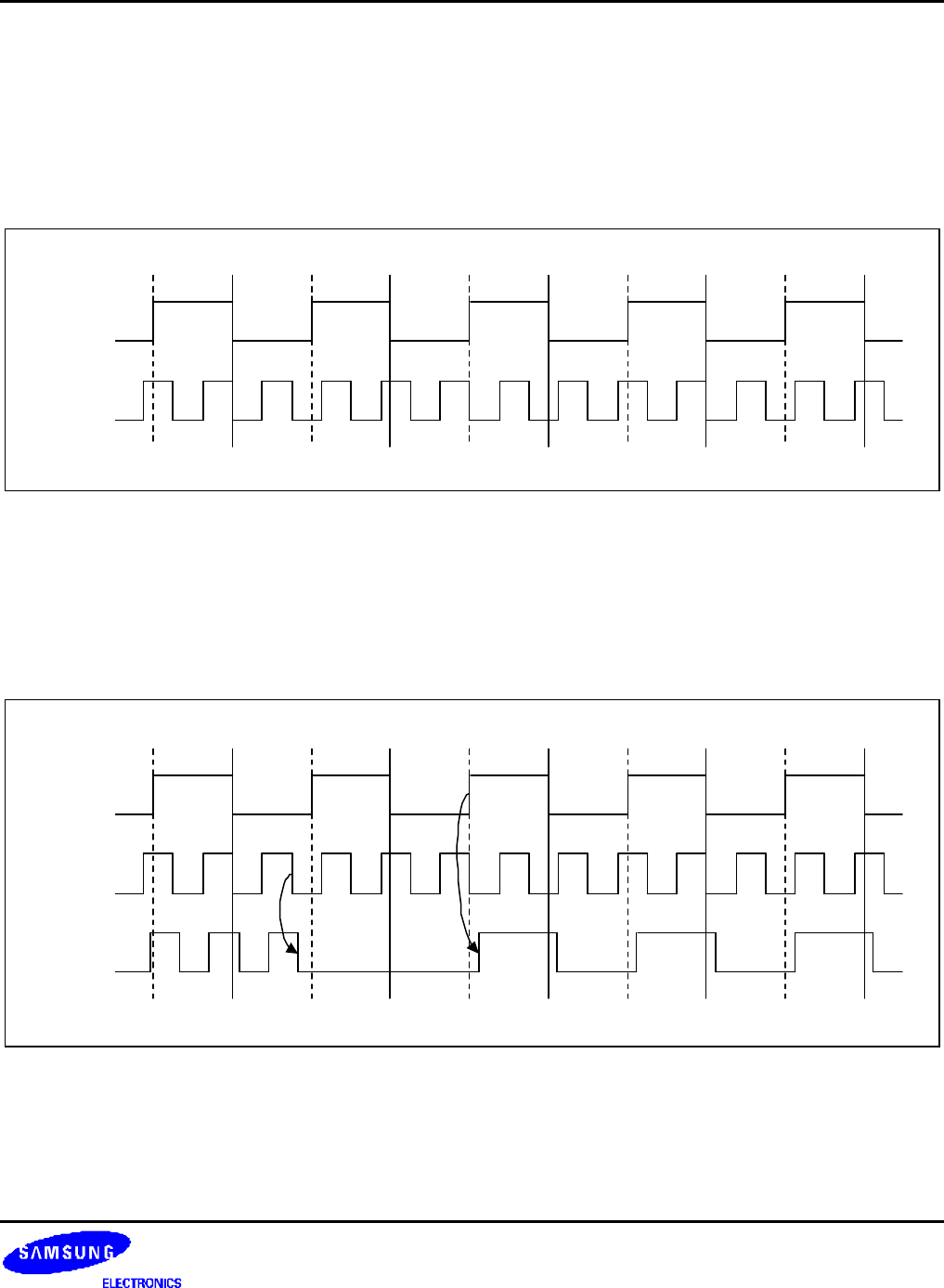

This mode is typically used in systems with low speed memory. In this mode of operation GCLK can be sourced

from BCLK and FCLK. BCLK is used to control the AMBA memory interface. FCLK is used to control the internal

ARM9TDMI processor core and any cache operations. The one restriction is that FCLK must have a higher frequency

than BCLK. An example is shown in Figure 5-4.

FCLK

BCLK

Figure 5-4. Asynchronous Clocking Mode

If the ARM920T performs an external access, for example, a cache miss or a cache line fill, ARM920T will switch to

BCLK to perform the access. The delay when switching from FCLK and BCLK is a minimum of one BCLK cycle, and

a maximum of one and a half BCLK cycles. An example of the clock switching is shown in Figure 5-4 . When

switching from BCLK to FCLK the minimum delay is one FCLK cycle and the maximum delay is one and a half

FCLK cycles. An example of the clock switching is shown in Figure 5-5.

FCLK

BCLK

ECLK

Figure 5-5. Switching from FCLK to BCLK in Asynchronous Mode