CLOCK & POWER MANAGEMENT S3C2410A

7-22

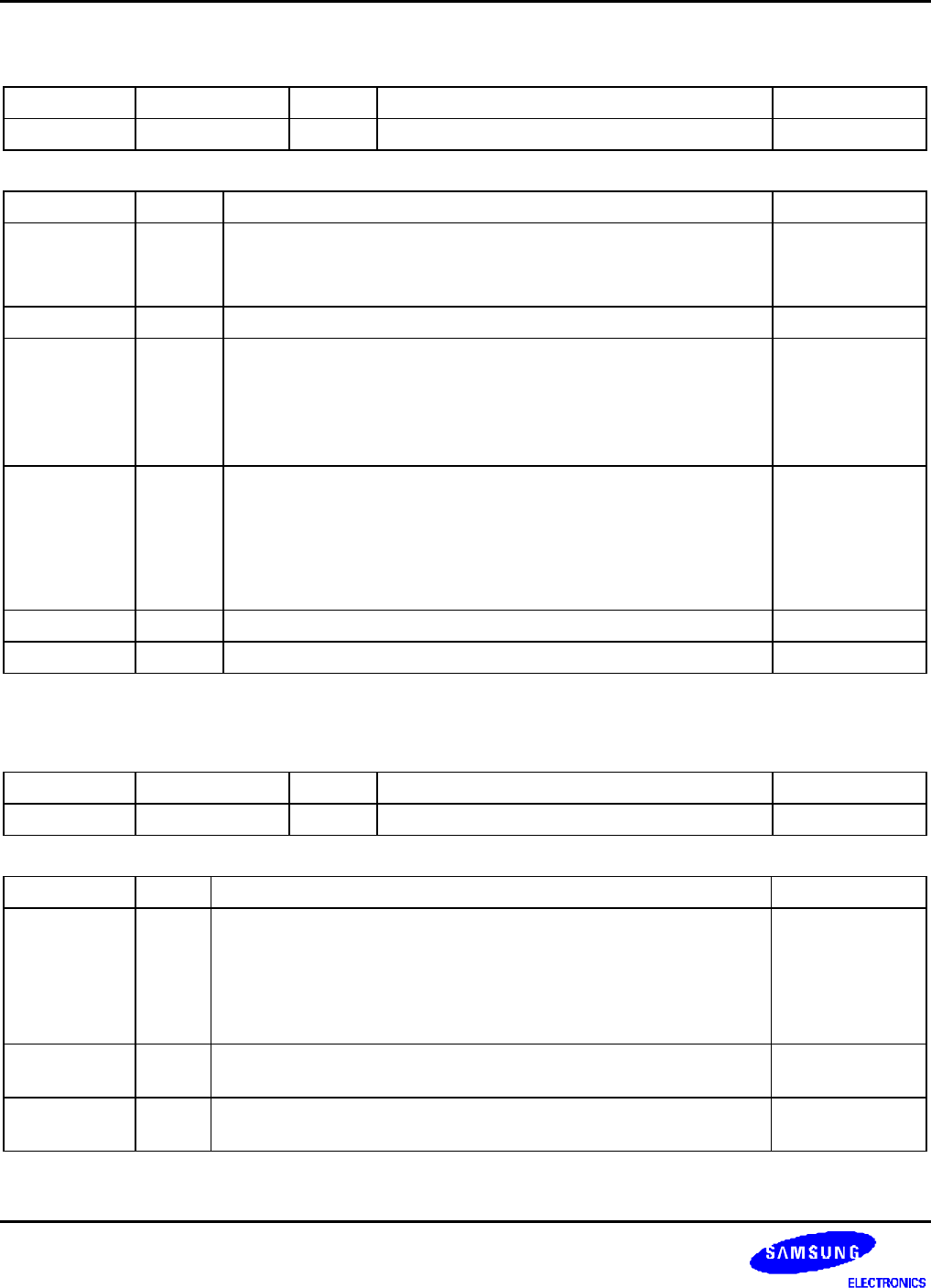

CLOCK SLOW CONTROL (CLKSLOW) REGISTER

Register Address R/W Description Reset Value

CLKSLOW 0x4C000010 R/W Slow clock control register 0x00000004

CLKSLOW Bit Description Initial State

UCLK_ON [7] 0: UCLK ON (UPLL is also turned on and the UPLL lock time is

inserted automatically.)

1: UCLK OFF (UPLL is also turned off.)

0

Reserved [6] Reserved –

MPLL_OFF [5] 0 : PLL is turned on.

After PLL stabilization time (minimum 150us), SLOW_BIT

can be cleared to 0.

1 : PLL is turned off.

PLL is turned off only when SLOW_BIT is 1.

0

SLOW_BIT [4] 0 : FCLK = Mpll (MPLL output)

1: SLOW mode

FCLK = input clock / (2 x SLOW_VAL) (SLOW_VAL > 0)

FCLK = input clock (SLOW_VAL = 0)

input clock = XTIpll or EXTCLK

0

Reserved [3] – –

SLOW_VAL [2:0] The divider value for the slow clock when SLOW_BIT is on. 0x4

CLOCK DIVIDER CONTROL (CLKDIVN) REGISTER

Register Address R/W Description Reset Value

CLKDIVN 0x4C000014 R/W Clock divider control register 0x00000000

CLKDIVN Bit Description Initial State

HDIVN1 [2] Special bus clock ratio available. (1:4:4)

0: Reserved

1: HCLK has the clock same as the FCLK/4.

PCLK has the clock same as the FCLK/4.

Note: If this bit is "0b1", HDIVN and PDIVN must be set "0b0".

0

HDIVN [1] 0: HCLK has the clock same as the FCLK.

1: HCLK has the clock same as the FCLK/2.

0

PDIVN [0] 0: PCLK has the clock same as the HCLK.

1: PCLK has the clock same as the HCLK/2.

0