MEMORY CONTROLLER S3C2410A

5-16

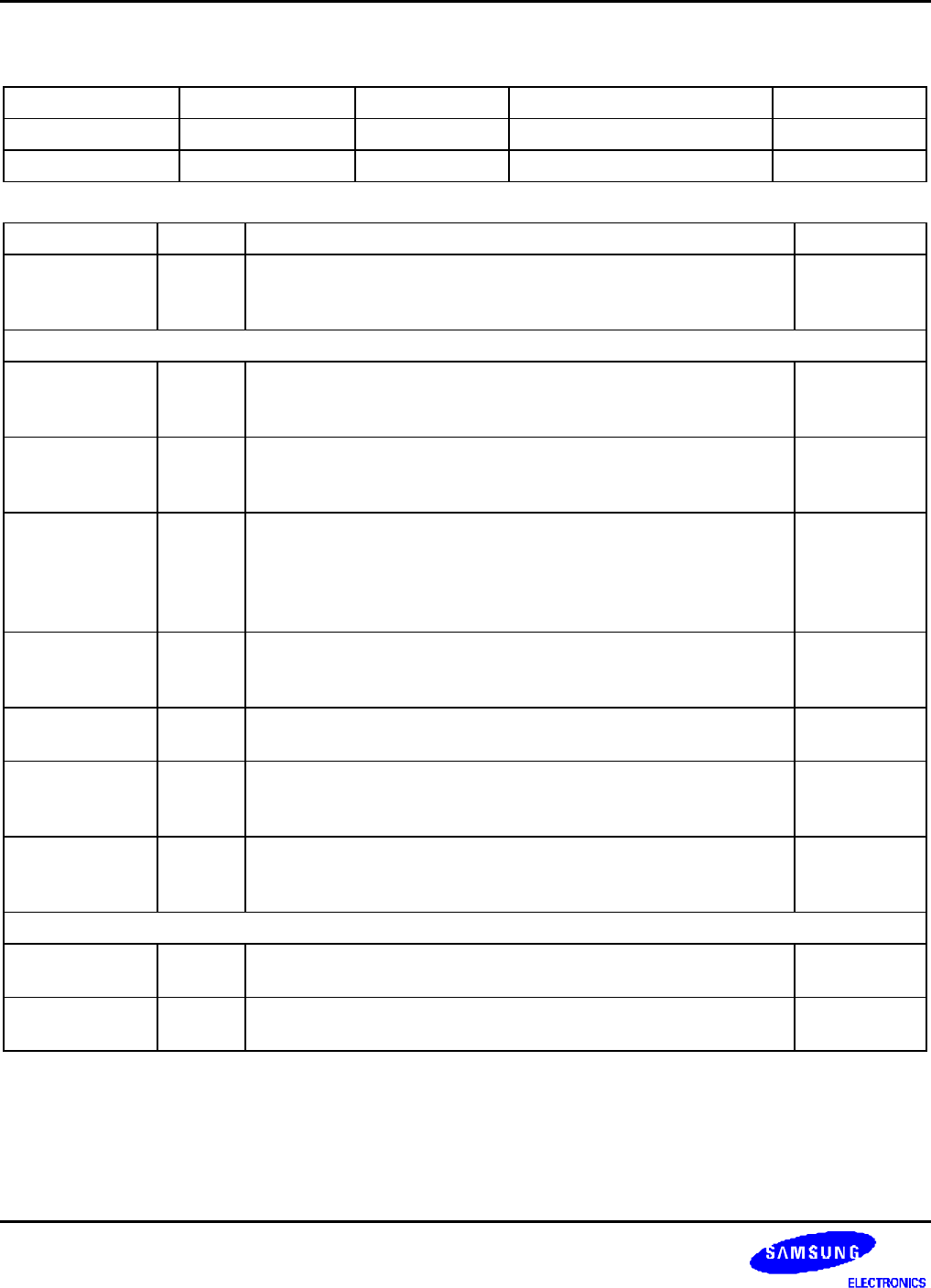

BANK CONTROL REGISTER (BANKCONn: nGCS6-nGCS7)

Register Address R/W Description Reset Value

BANKCON6 0x4800001C R/W Bank 6 control register 0x18008

BANKCON7 0x48000020 R/W Bank 7 control register 0x18008

BANKCONn Bit Description Initial State

MT [16:15] Determine the memory type for bank6 and bank7.

00 = ROM or SRAM 01 = Reserved (Do not use)

10 = Reserved (Do not use) 11 = Sync. DRAM

11

Memory Type = ROM or SRAM [MT=00] (15-bit)

Tacs [14:13] Address set-up time before nGCS

00 = 0 clock 01 = 1 clock 10 = 2 clocks 11 = 4

clocks

00

Tcos [12:11] Chip selection set-up time before nOE

00 = 0 clock 01 = 1 clock 10 = 2 clocks 11 = 4

clocks

00

Tacc [10:8] Access cycle

000 = 1 clock 001 = 2 clocks

010 = 3 clocks 011 = 4 clocks

100 = 6 clocks 101 = 8 clocks

110 = 10 clocks 111 = 14 clocks

111

Tcoh [7:6] Chip selection hold time after nOE

00 = 0 clock 01 = 1 clock

10 = 2 clocks 11 = 4 clocks

00

Tcah [5:4] Address hold time after nGCSn

00 = 0 clock 01 = 1clock 10 = 2 clocks 11 = 4 clocks

00

Tacp [3:2]

Page mode access cycle @ Page mode

00 = 2 clocks 01 = 3 clocks

10 = 4 clocks 11 = 6 clocks

00

PMC [1:0] Page mode configuration

00 = normal (1 data) 01 = 4 consecutive accesses

10 = 8 consecutive accesses 11 = 16 consecutive accesses

00

Memory Type = SDRAM [MT=11] (4-bit)

Trcd [3:2] RAS to CAS delay

00 = 2 clocks 01 = 3 clocks 10 = 4 clocks

10

SCAN [1:0] Column address number

00 = 8-bit 01 = 9-bit 10= 10-bit

00