SPI INTERFACE S3C2410A

22-2

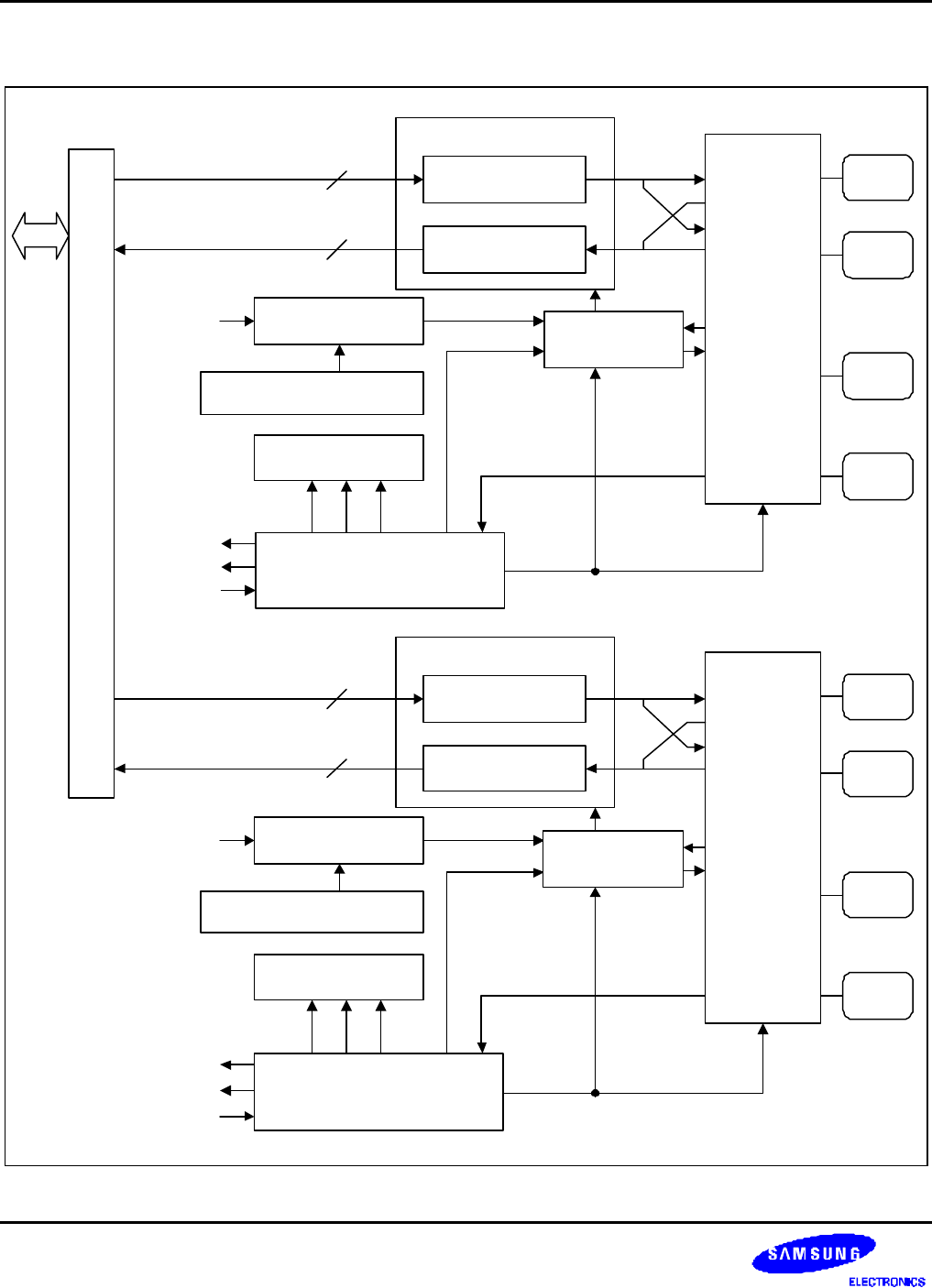

BLOCK DIAGRAM

8bit Prescaler 1PCLK

Status Register 1

Prescaler Register 1

/SS

nSS 0

SCK

SPICLK 0

MOSI

SPIMOSI 0

MISO

SPIMISO 0

Pin Control Logic 0

MSTR

Tx 8bit Shift Reg 0

Rx 8bit Shift Reg 0

LSB

MSB LSB

MSB

8

8

Clock

SPI Clock

(Master)

CPOL

CPHA

CLOCK Logic 0

MULF

DCOL

REDY

APB I/F 0

(INT DMA 0)

Slave

Data

Bus

INT 0 / INT 1

REQ0 / REQ1

ACK0 / ACK1

/SS

nSS 1

SCK

SPICLK 1

MOSI

SPIMOSI 1

MISO

SPIMISO 1

Pin Control Logic 1

MSTR

Tx 8bit Shift Reg 1

Rx 8bit Shift Reg 1

LSB

MSB LSB

MSB

8

8

Clock

SPI Clock

(Master)

CPOL

CPHA

MULF

DCOL

REDY

Slave

Slave

INT 0 / INT 1

REQ0 / REQ1

ACK0 / ACK1

8bit Prescaler 0PCLK

Status Register 0

Prescaler Register 0

Master

Slave

Master

Slave

Master

Slave

Master

Slave

Master

Slave

Master

CLOCK Logic 1

APB I/F 1

(INT DMA 1)

Figure 22-1. SPI Block Diagram