PROGRAMMER'S MODEL ARM920T PROCESSOR

2-16

The function of each cache operation is selected by the opcode_2 and CRm fields in the MCR instruction used to

write CP15 register 7. Writing other opcode_2 or CRm values is unpredictable.

Reading from CP15 register 7 is unpredictable.

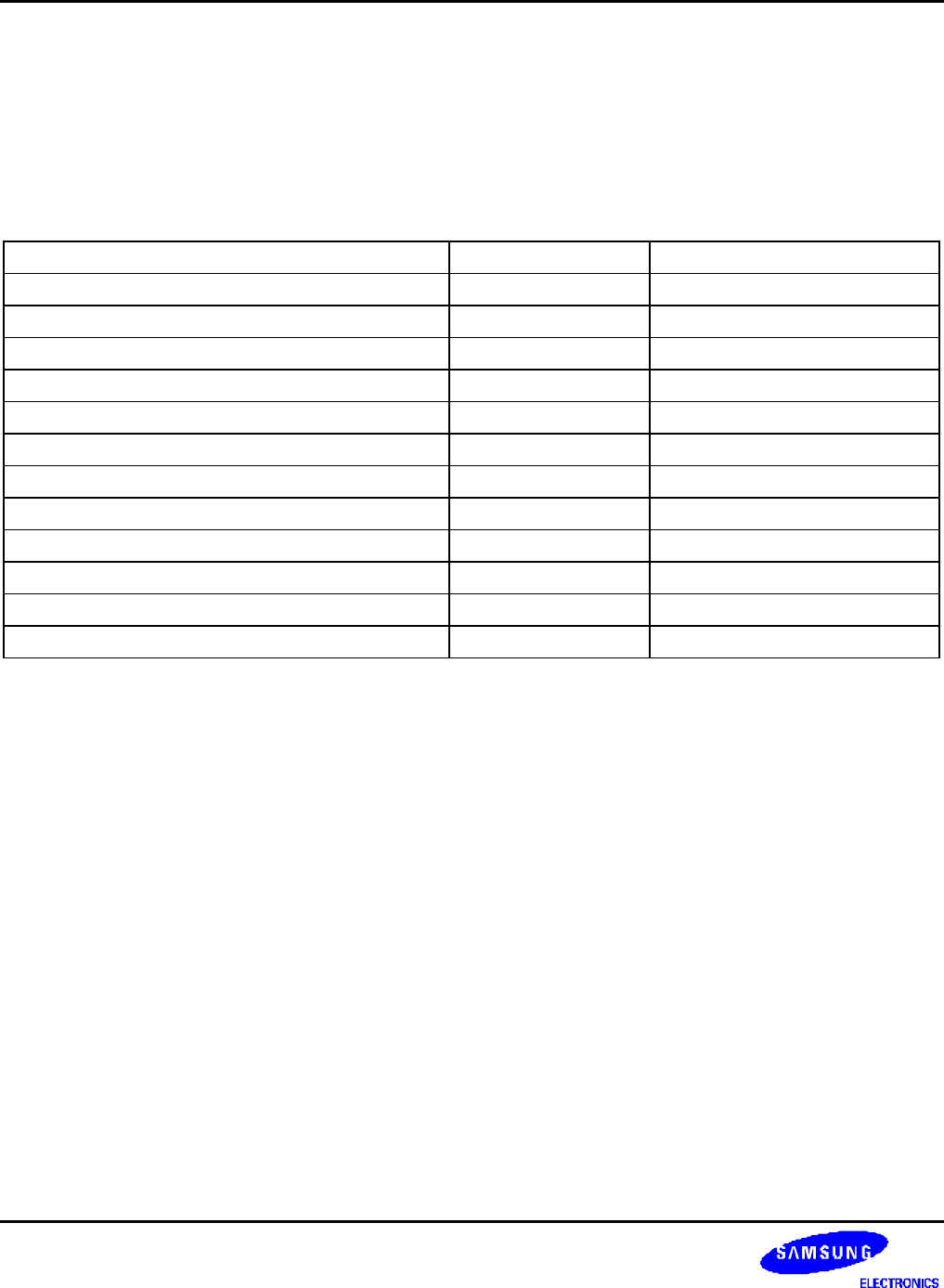

Table 2-16 on page 2-16 shows instructions that can be used to perform cache operations with register 7

Table 2-16. Cache Operations Register 7

Function Data Instruction

Invalidate ICache & DCache SBZ MCR p15,0,Rd,c7,c7,0

Invalidate ICache SBZ MCR p15,0,Rd,c7,c5,0

Invalidate ICache single entry (using MVA) MVA format MCR p15,0,Rd,c7,c5,1

Prefetch ICache line (using MVA) MVA format MCR p15,0,Rd,c7,c13,1

Invalidate DCache SBZ MCR p15,0,Rd,c7,c6,0

Invalidate DCache single entry (using MVA) MVA format MCR p15,0,Rd,c7,c6,1

Clean DCache single entry (using MVA) MVA format MCR p15,0,Rd,c7,c10,1

Clean and Invalidate DCache entry (using MVA) MVA format MCR p15,0,Rd,c7,c14,1

Clean DCache single entry (using index) Index format MCR p15,0,Rd,c7,c10,2

Clean and Invalidate DCache entry (using index) Index format MCR p15,0,Rd,c7,c14,2

Drain write buffer (1) SBZ MCR p15,0,Rd,c7,c10,4

Wait for interrupt (2) SBZ MCR p15,0,Rd,c7,c0,4

NOTES:

1. Will stop execution until the write buffer has drained.

2. Will stop execution in a LOW power state until an interrupt occurs.