MMC/SD/SDIO HOST CONTROLLER S3C2410A

19-10

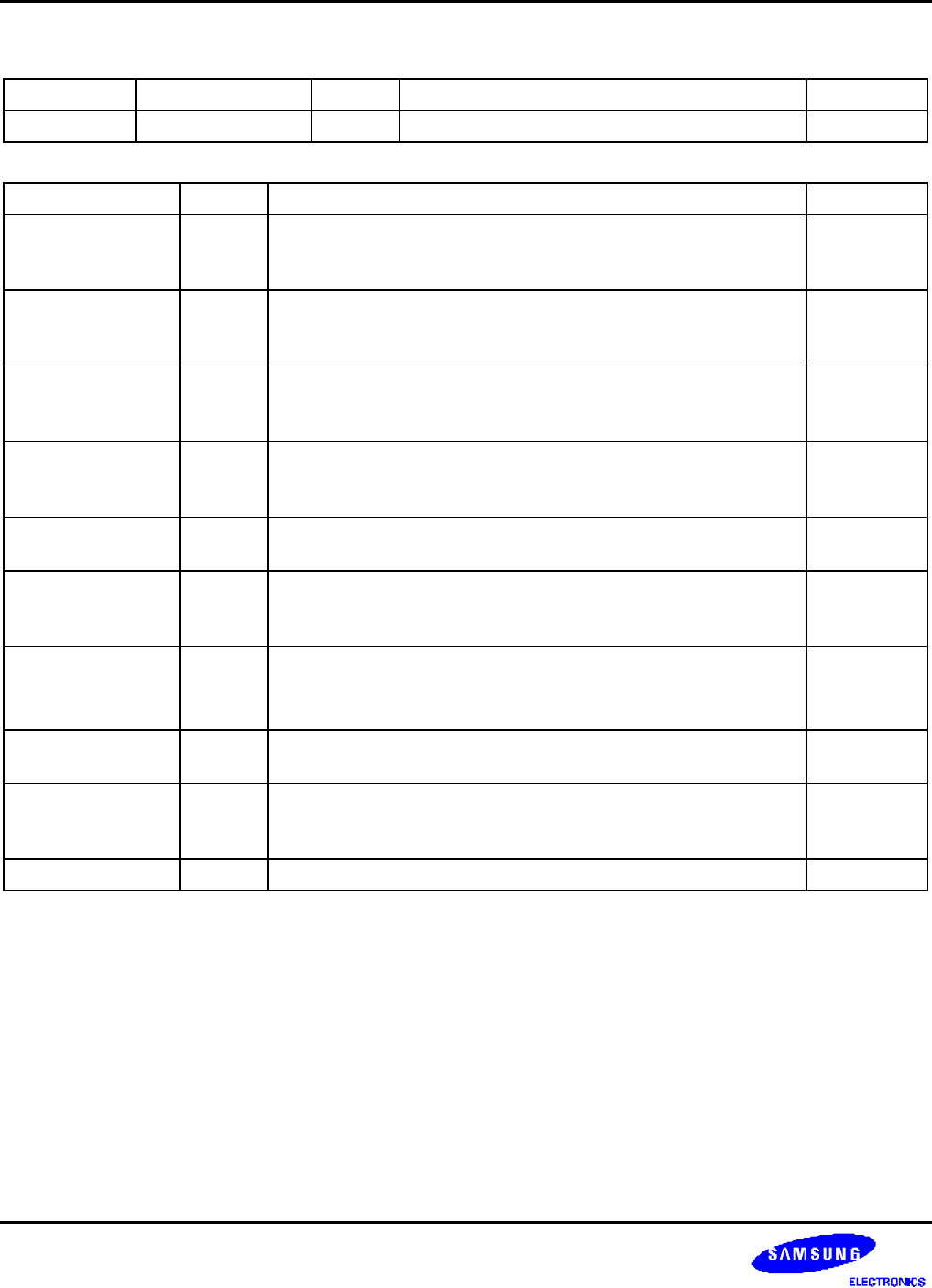

SDI Data Control (SDIDCON) Register

Register Address R/W Description Reset Value

SDIDCON 0x5A00002C R/W SDI data control register 0x0

SDIDCON Bit Description Initial Value

SDIO Interrupt

Period Type

(PrdType)

[21] Determine whether SDIO Interrupt period is 2 cycle or extend

more cycle when last data block is transferred (for SDIO).

0 = exactly 2 cycle, 1 = more cycles(like single block)

0

Transmit After

Response (TARSP)

[20] Determine when data transmit start after response receive or not.

0 = directly after DatMode set,

1 = after response receive(assume DatMode sets to 2'b11)

0

Receive After

Command

(RACMD)

[19] Determine when data receive start after command sent or not.

0 = directly after DatMode set,

1 = after command sent (assume DatMode sets to 2'b10)

0

Busy After

Command

(BACMD)

[18] Determine when busy receive start after command sent or not.

0 = directly after DatMode set,

1 = after command sent (assume DatMode sets to 2'b01)

0

Block mode

(BlkMode)

[17] Data transfer mode.

0 = stream data transfer, 1 = block data transfer

0

Wide bus enable

(WideBus)

[16] Determine enable wide bus mode.

0 = standard bus mode(only SDIDAT[0] used),

1 = wide bus mode(SDIDAT[3:0] used)

0

DMA Enable

(EnDMA)

[15] Enable DMA.

0 = disable(polling), 1 = dma enable

When DMA operation is completed, this bit should be disabled.

0

Stop by force

(STOP)

[14] Determine whether data transfer stop by force or not.

0 = normal, 1 = stop by force

0

Data Transfer Mode

(DatMode)

[13:12] Determine the direction of data transfer.

00 = ready, 01 = only busy check start

10 = data receive start, 11 = data transmit start

00

BlkNum [11:0] Block Number (0~4095). Do not care when stream mode. 0x000

NOTES:

1. If you want one of TARSP, RACMD and BACMD bits (SDIDCON[20:18]) to "1", you need to write on SDIDCON

register head of on SDICCON register (always need for SDIO).

2. When DMA operation is completed, DMA Enable[15] bit of SDIDCON register should be disabled.