S3C2410A CLOCK & POWER MANAGEMENT

7-11

NORMAL Mode

In normal mode, all peripherals and the basic blocks including power management block, the CPU core, the bus

controller, the memory controller, the interrupt controller, DMA, and the external master may operate fully. But, the

clock to each peripheral, except the basic blocks, can be stopped selectively by software to reduce the power

consumption.

IDLE Mode

In IDLE mode, the clock to the CPU core is stopped except the bus controller, the memory controller, the interrupt

controller, and the power management block. To exit the IDLE mode, EINT[23:0], or RTC alarm interrupt, or the other

interrupts should be activated. (EINT is not available until GPIO block is turned on).

SLOW Mode (Non-PLL Mode)

Power consumption can be reduced in the SLOW mode by applying a slow clock and excluding the power

consumption from the PLL. The FCLK is the frequency of divide_by_n of the input clock (XTIpll or EXTCLK) without

PLL. The divider ratio is determined by SLOW_VAL in the CLKSLOW control register and CLKDIVN control register.

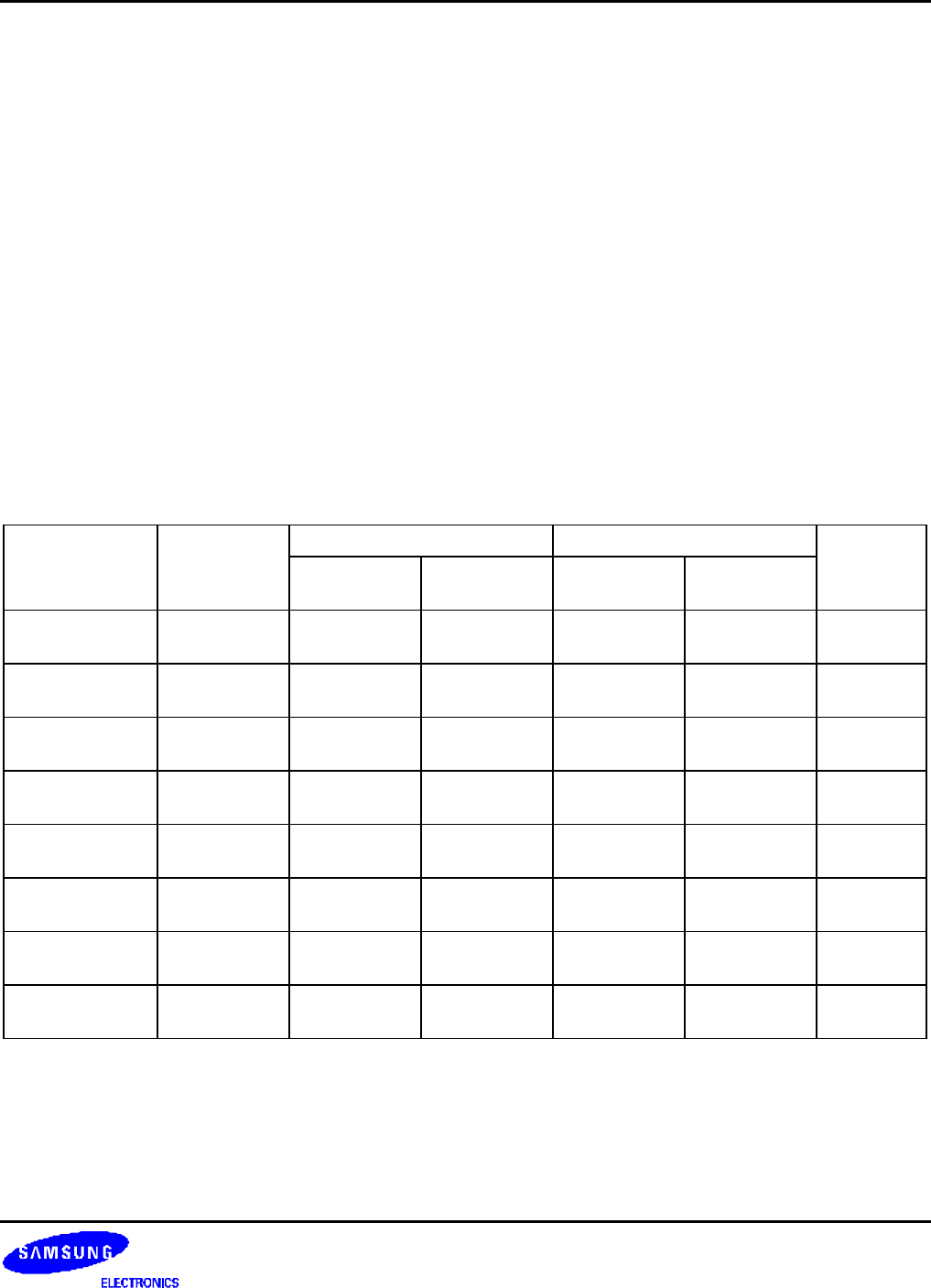

Table 7-3. CLKSLOW and CLKDIVN Register Settings for SLOW Clock

SLOW_VAL FCLK HCLK PCLK UCLK

1/1 Option

(HDIVN = 0)

1/2 Option

(HDIVN = 1)

1/1 Option

(PDIVN = 0)

1/2 Option

(PDIVN = 1)

0 0 0 EXTCLK or

XTIpll / 1

EXTCLK or

XTIpll / 1

EXTCLK or

XTIpll / 2

HCLK HCLK / 2 48 MHz

0 0 1 EXTCLK or

XTIpll / 2

EXTCLK or

XTIpll / 2

EXTCLK or

XTIpll / 4

HCLK HCLK / 2 48 MHz

0 1 0 EXTCLK or

XTIpll / 4

EXTCLK or

XTIpll / 4

EXTCLK or

XTIpll / 8

HCLK HCLK / 2 48 MHz

0 1 1 EXTCLK or

XTIpll / 6

EXTCLK or

XTIpll / 6

EXTCLK or

XTIpll / 12

HCLK HCLK / 2 48 MHz

1 0 0 EXTCLK or

XTIpll / 8

EXTCLK or

XTIpll / 8

EXTCLK or

XTIpll / 16

HCLK HCLK / 2 48 MHz

1 0 1 EXTCLK or

XTIpll / 10

EXTCLK or

XTIpll / 10

EXTCLK or

XTIpll / 20

HCLK HCLK / 2 48 MHz

1 1 0 EXTCLK or

XTIpll / 12

EXTCLK or

XTIpll / 12

EXTCLK or

XTIpll / 24

HCLK HCLK / 2 48 MHz

1 1 1 EXTCLK or

XTIpll / 14

EXTCLK or

XTIpll / 14

EXTCLK or

XTIpll / 28

HCLK HCLK / 2 48 MHz

In SLOW mode, PLL will be turned off to reduce the PLL power consumption. When the PLL is turned off in the

SLOW mode and the user changes power mode from SLOW mode to NORMAL mode, the PLL needs clock

stabilization time (PLL lock time). This PLL stabilization time is automatically inserted by the internal logic with lock

time count register. The PLL stability time will take 150us after the PLL is turned on. During PLL lock time, the FCLK

becomes SLOW clock.