S3C2410A THUMB INSTRUCTION SET

4-33

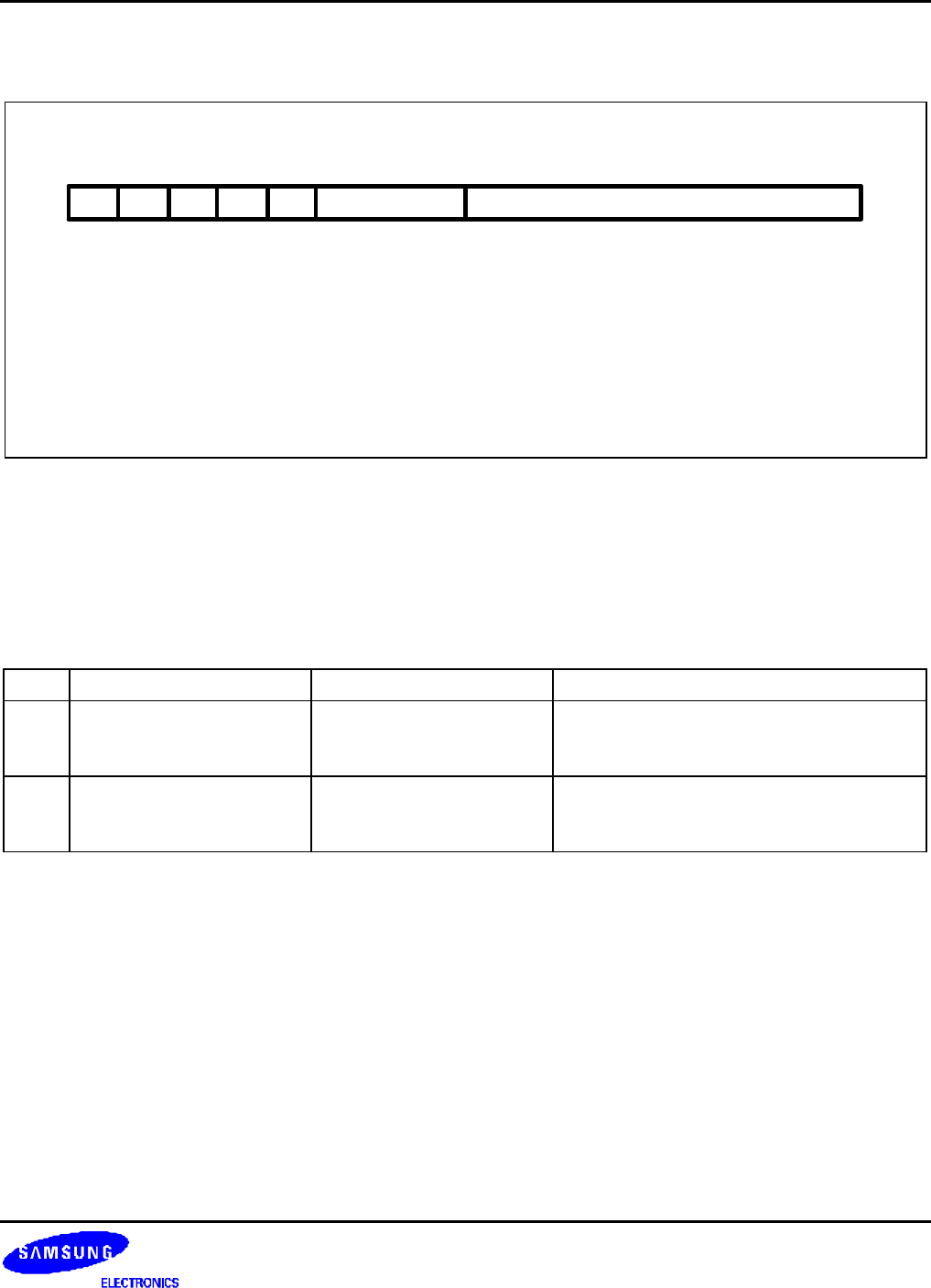

FORMAT 15: MULTIPLE LOAD/STORE

[7:0] Register List

[10:8] Base Register

[11] Load/Store Bit

0 = Store to memory

1 = Load from memory

15 0

1

14

10

1 0

13 12

11

Rlist0 L

78

Rb

Figure 4-16. Format 15

OPERATION

These instructions allow multiple loading and storing of Lo registers. The THUMB assembler syntax is shown in the

following table.

Table 4-16. The Multiple Load/Store Instructions

L THUMB assembler ARM equivalent Action

0 STMIA Rb!, { Rlist } STMIA Rb!, { Rlist } Store the registers specified by Rlist, starting

at the base address in Rb. Write back the

new base address.

1 LDMIA Rb!, { Rlist } LDMIA Rb!, { Rlist } Load the registers specified by Rlist, starting

at the base address in Rb. Write back the

new base address.

INSTRUCTION CYCLE TIMES

All instructions in this format have an equivalent ARM instruction as shown in Table 4-16. The instruction cycle times

for the THUMB instruction are identical to that of the equivalent ARM instruction.

EXAMPLES

STMIA R0!, {R3-R7} ; Store the contents of registers R3-R7

; starting at the address specified in

; R0, incrementing the addresses for each word.

; Write back the updated value of R0.