USB DEVICE S3C2410A

13-12

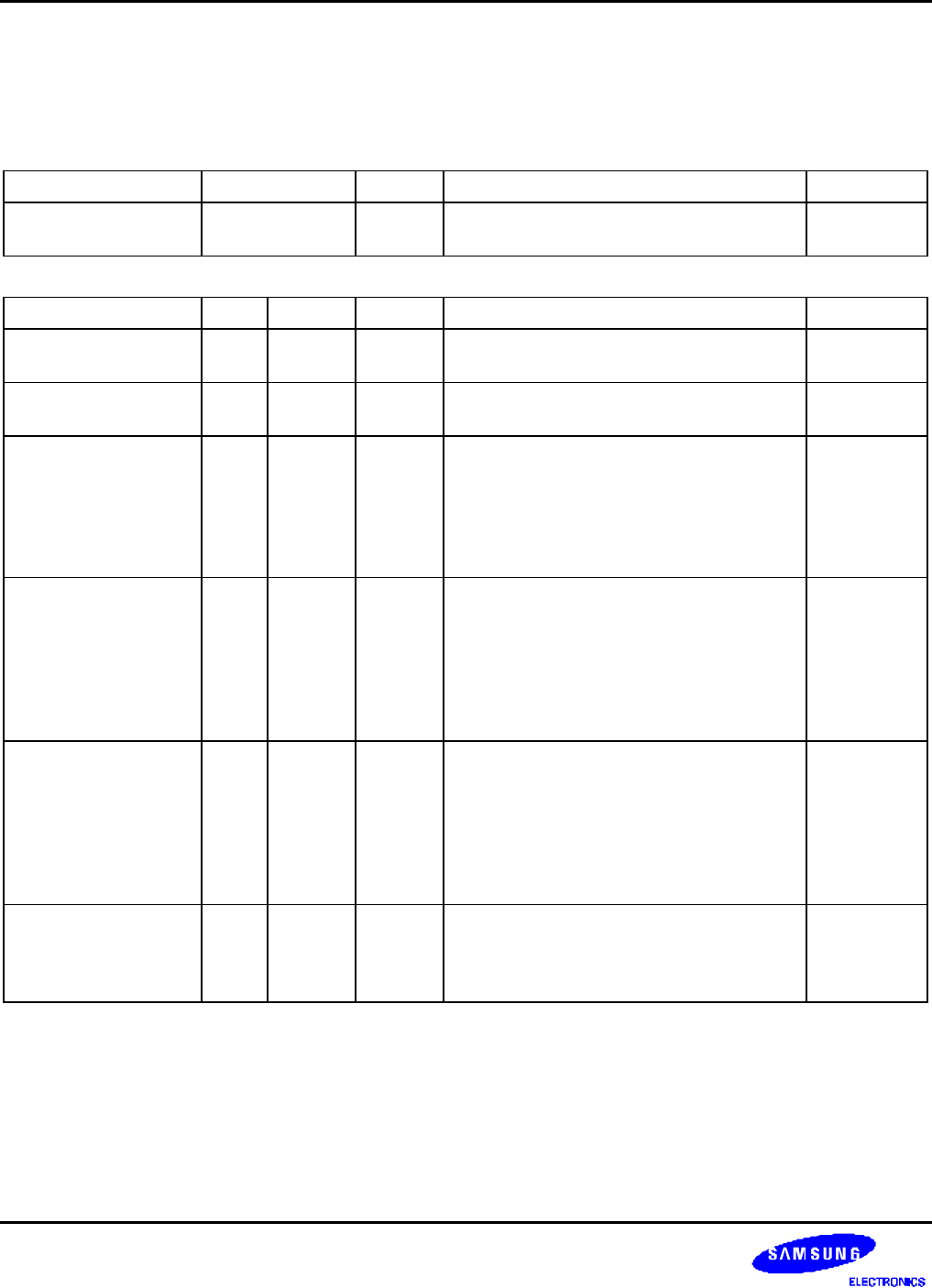

END POINT0 CONTROL STATUS REGISTER (EP0_CSR)

This register has the control and status bits for Endpoint 0. Since a control transaction is involved with both IN and

OUT tokens, there is only one CSR register, mapped to the IN CSR1 register. (share IN1_CSR and can access by

writing index register "0" and read/write IN1_CSR)

Register Address R/W Description Reset Value

EP0_CSR 0x52000184(L)

0x52000187(B)

R/W

(byte)

Endpoint 0 status register 0x00

EP0_CSR Bit MCU USB Description Initial State

SERVICED_SETUP_E

ND

[7] W CLEAR The MCU should write a "1" to this bit to

clear SETUP_END.

0

SERVICED_OUT_

PKT_RDY

[6] W CLEAR The MCU should write a "1" to this bit to

clear OUT_PKT_RDY.

0

SEND_STALL [5] R/W CLEAR MCU should write a "1" to this bit at the

same time it clears OUT_PKT_RDY, if it

decodes an invalid token.

0 = Finish the STALL condition

1 = The USB issues a STALL and shake to

the current control transfer.

0

SETUP_END [4] R SET Set by the USB when a control transfer

ends before DATA_END is set.

When the USB sets this bit, an interrupt is

generated to the MCU.

When such a condition occurs, the USB

flushes the FIFO and invalidates MCU

access to the FIFO.

0

DATA_END [3] SET CLEAR Set by the MCU on the conditions below:

1. After loading the last packet of data into

the FIFO, at the same time IN_PKT_RDY is

set.

2. While it clears OUT_PKT_RDY after

unloading the last packet of data.

3. For a zero length data phase.

0

SENT_STALL [2] CLEAR SET Set by the USB if a control transaction is

stopped due to a protocol violation. An

interrupt is generated when this bit is set.

The MCU should write "0" to clear this bit.

0