S3C2410A CLOCK & POWER MANAGEMENT

7-5

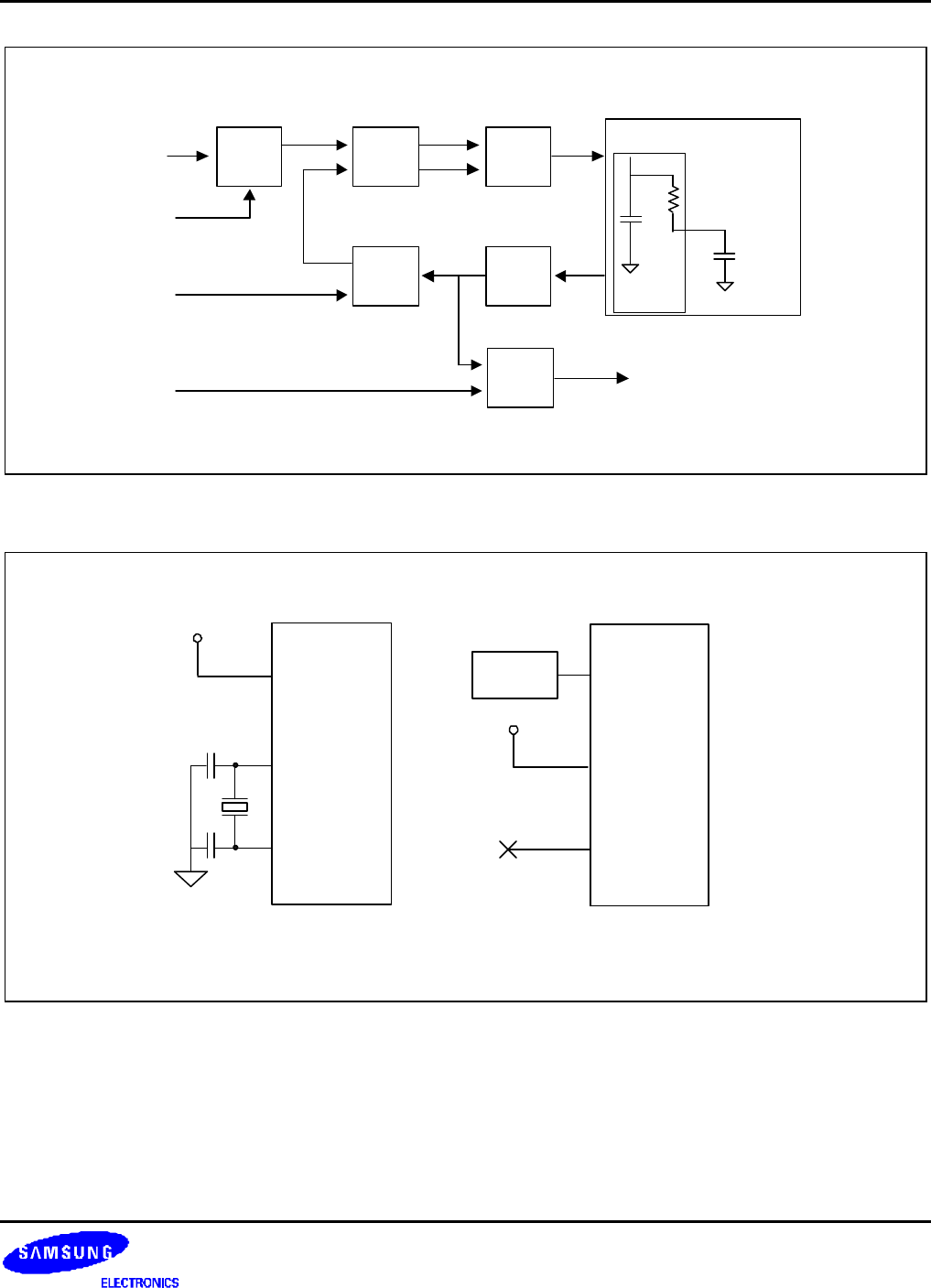

Divider

P

Loop Filter

Fin

M[7:0]

S[1:0]

PFD

Divider

M

P[5:0]

F

vco

PUMP

VCO

Divider

S

F

ref

MPLL,UPLL

R

C

Internal

5 pF

External

MPLLCAP,

UPLLCAP

Figure 7-2. PLL (Phase-Locked Loop) Block Diagram

EXTCLK

XTIpll

XTOpll

EXTCLK

XTIpll

XTOpll

External

OSC

a) X-TAL Oscillation (OM[3:2]=00) b) External Clock Source (OM[3:2]=11)

V

DD

V

DD

Figure 7-3. Main Oscillator Circuit Examples