PROGRAMMER'S MODEL ARM920T PROCESSOR

2-14

REGISTER 4: RESERVED

Accessing (reading or writing) this register will cause unpredictable behavior.

REGISTER 5: FAULT STATUS REGISTERS

Register 5 is the fault status register (FSR). The FSR contains the source of the last data fault, indicating the domain

and type of access being attempted when the data abort occurred.

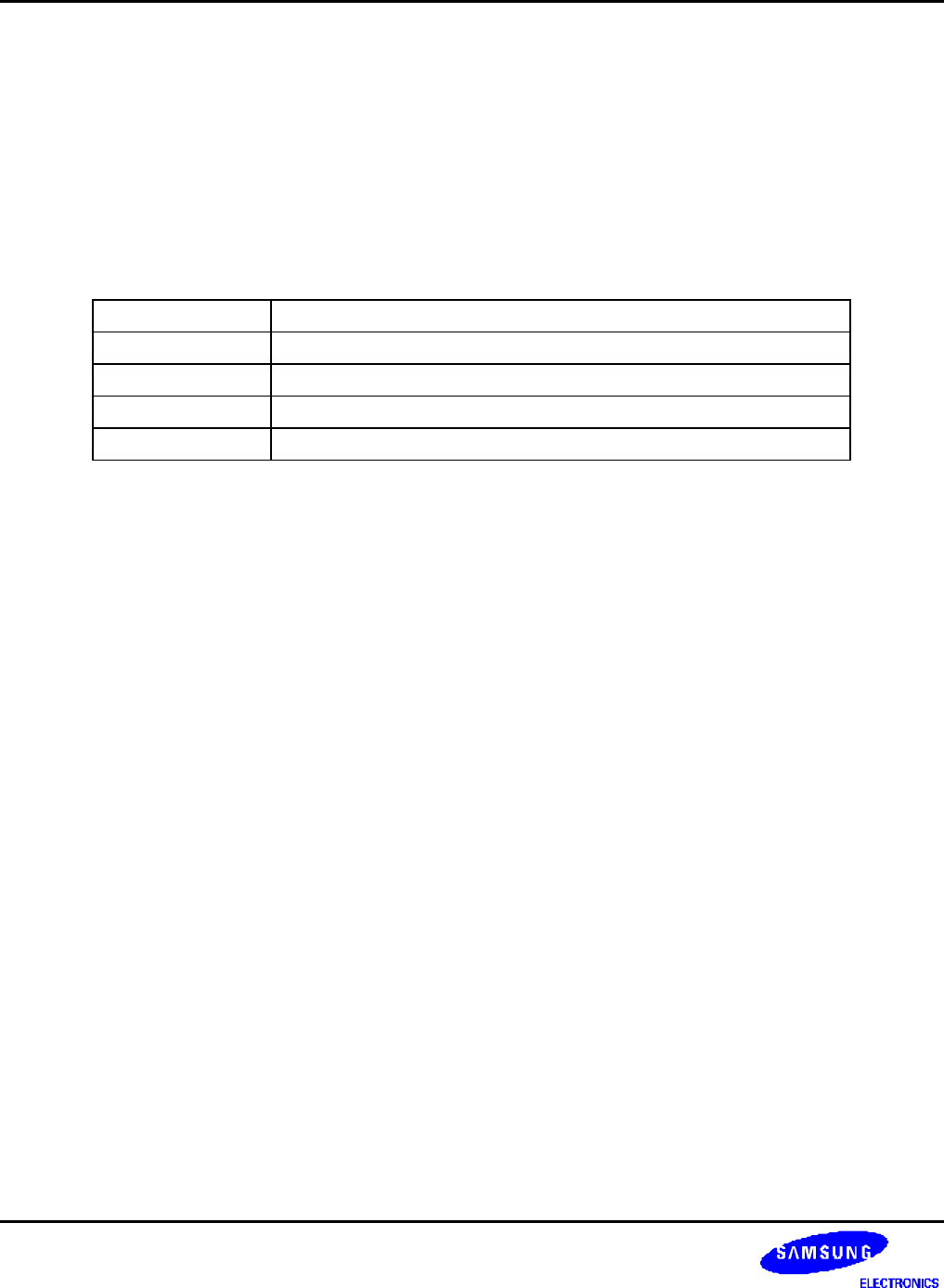

Table 2-14. Fault Status Register

Register Bits Description

31:9 UNP when read/SBZ for write.

8 0 when read/SBZ for write.

7:4 Domain being accessed when fault occurred (D15-D0).

3:0 Fault type.

The fault type encoding is shown in Fault address and fault status registers on page 3-18.

The data FSR is defined in ARM architecture v4T. Additionally, a pipelined prefetch FSR is available, for debug

purposes only. The pipeline matches that of the ARM9TDMI.

The following instructions can be used to access the data and prefetch FSR:

MRC p15, 0, Rd, c5, c0, 0 ;read data FSR value

MCR p15, 0, Rd, c5, c0, 0 ;write data FSR value

MRC p15, 0, Rd, c5, c0, 1 ;read prefetch FSR value

MCR p15, 0, Rd, c5, c0, 1 ;write prefetch FSR value

The ability to write to the FSR is useful for a debugger to restore the value of the FSR. The register should be written

using the read-modify-write method. Bits[31:8] should be zero.