ARM920T PROCESSOR CACHES, WRITE BUFFER

4-7

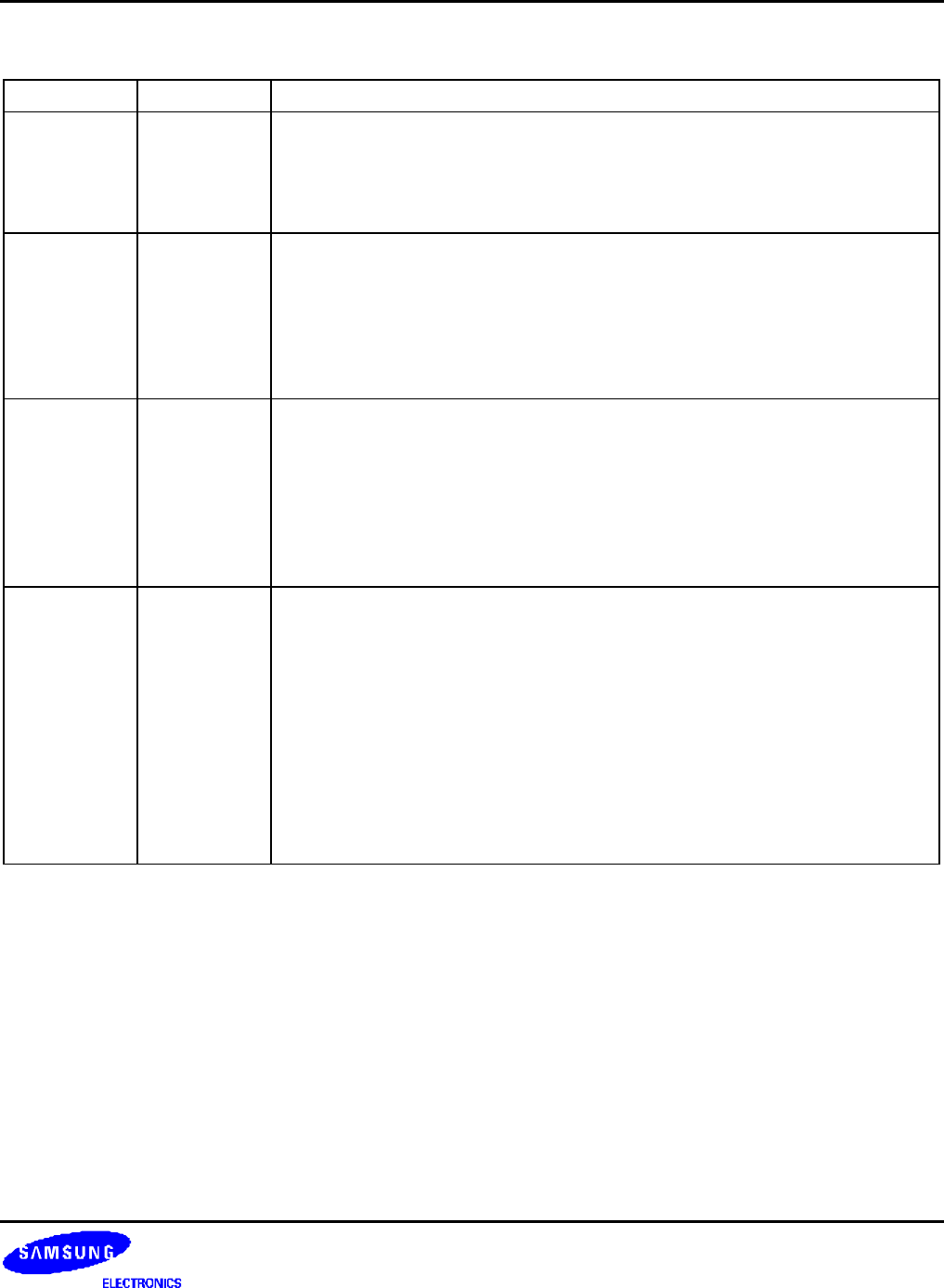

Table 4-1. Data Cache and Write Buffer Configuration

Ctt and Ccr Btt Data cache, write buffer and memory access behavior

0 (1) 0 Non-cached, non-buffered (NCNB)

Reads and writes are not cached and always perform accesses on the ASB and

may be externally aborted.

Writes are not buffered. The CPU halts until the write is completed on the ASB.

Cache hits should never occur. (2)

0 1 Non-cached buffered (NCB)

Reads and writes are not cached, and always perform accesses on the ASB.

Cache hits should never occur.

Writes are placed in the write buffer and will appear on the ASB. The CPU

continues execution as soon as the write is placed in the write buffer.

Reads may be externally aborted.

Writes can not be externally aborted.

1 0 Cached, write-through mode (WT)

Reads which hit in the cache will read the data from the cache and do not

perform an access on the ASB.

Reads which miss in the cache cause a linefill.

All writes are placed in the write buffer and will appear on the ASB. The CPU

continues execution as soon as the write is placed in the write buffer.

Writes which hit in the cache update the cache.

Writes cannot be externally aborted.

1 1 Cached, write-back mode (WB)

Reads which hit in the cache will read the data from the cache and do not

perform an ASB access.

Reads which miss in the cache cause a linefill.

Writes which miss in the cache are placed in the write buffer and will appear on

the ASB. The CPU continues execution as soon as the write is placed in the

write buffer.

Writes which hit in the cache update the cache and mark the appropriate half of

the cache line as dirty, and do not cause an ASB access.

Cache write-backs are buffered.

Writes (Cache write-misses and cache write-backs) cannot be externally

aborted.

NOTES:

1. The control register C bit (Ccr) being zero disables all lookups in the cache, while the translation table descriptor C bit

(Ctt) being zero only stops new data being loaded into the cache. With Ccr = 1 and Ctt = 0 the cache will still be

searched

on every access to check whether the cache contains an entry for the data.

2. It is an operating system software error if a cache hit occurs when reading from, or writing to, a region of memory

marked as NCNB or NCB. The only way this can occur is if the operating system changes the value of the C and B bits

in a page table descriptor, while the cache contains data from the area of virtual memory controlled by that descriptor.

The cache and memory system behavior resulting from changing the page table descriptor in this way is unpredictable.

If the operating system needs to change the C and B bits of a page table descriptor, it must ensure that the caches do

not contain any data controlled by that descriptor. In some circumstances, the operating system may need to clean and

flush the caches to ensure this.