S3C2410A NAND FLASH CONTROLLER

6-3

AUTO BOOT MODE SEQUENCE

1. Reset is completed.

2. When the auto boot mode is enabled, the first 4 KBytes of NAND flash memory is copied onto Steppingstone 4-

KB internal buffer.

3. The Steppingstone is mapped to nGCS0.

4. CPU starts to execute the boot code on the Steppingstone 4-KB internal buffer.

NOTE

In the auto boot mode, ECC is not checked. So, The first 4 KBytes of NAND flash should have no bit error.

NAND FLASH MODE CONFIGURATION

1. Set NAND flash configuration by NFCONF register.

2. Write NAND flash command onto NFCMD register.

3. Write NAND flash address onto NFADDR register.

4. Read/Write data while checking NAND flash status by NFSTAT register. R/nB signal should be checked before

read operation or after program operation.

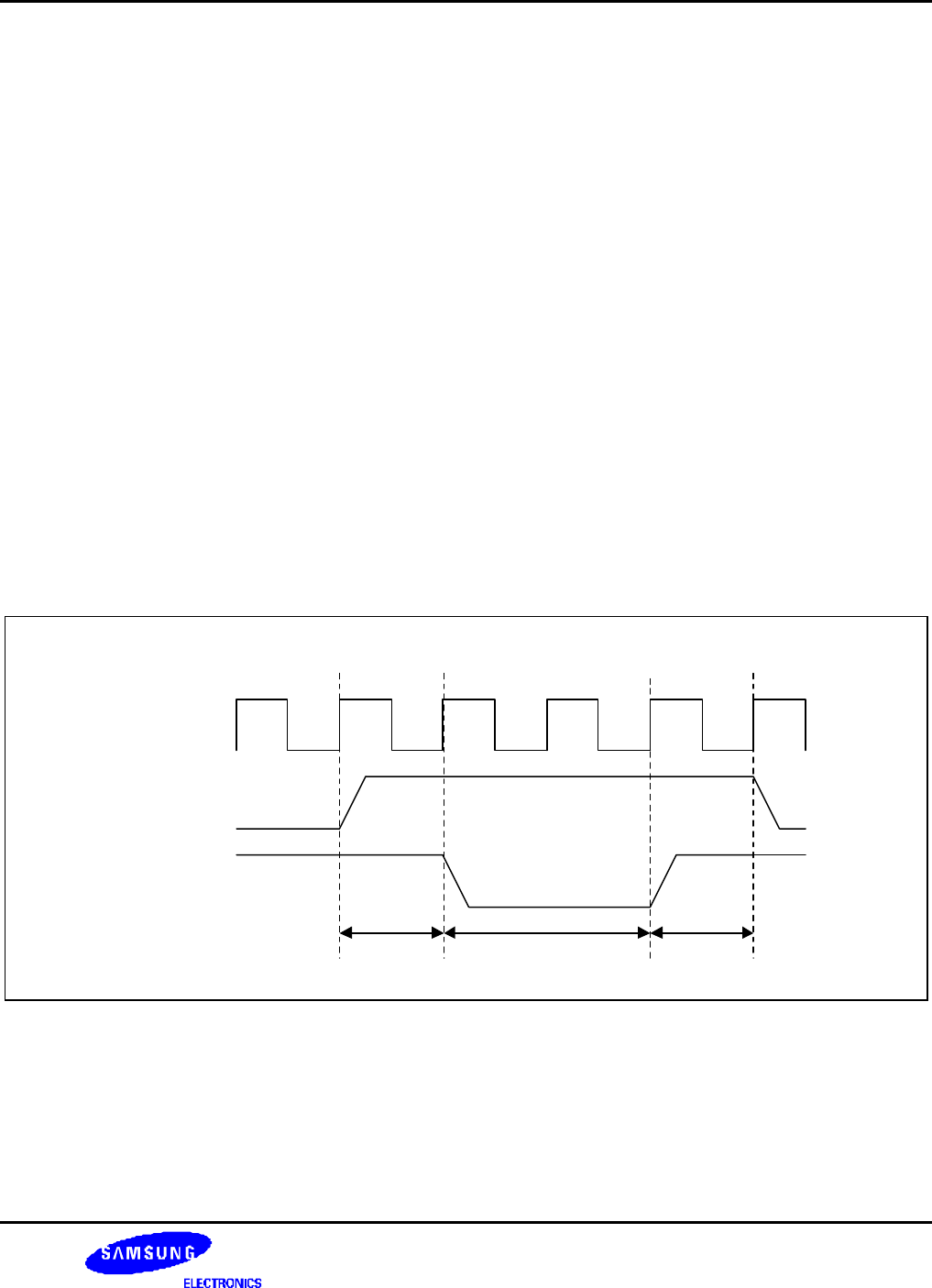

NAND FLASH MEMORY TIMING

CLE/ALE

HCLK

TACLS TWRPH1TWRPH0

nWE

Figure 6-3. TACLS = 0, TWRPH0 = 1, TWRPH1 = 0