S3C2410A UART

11-13

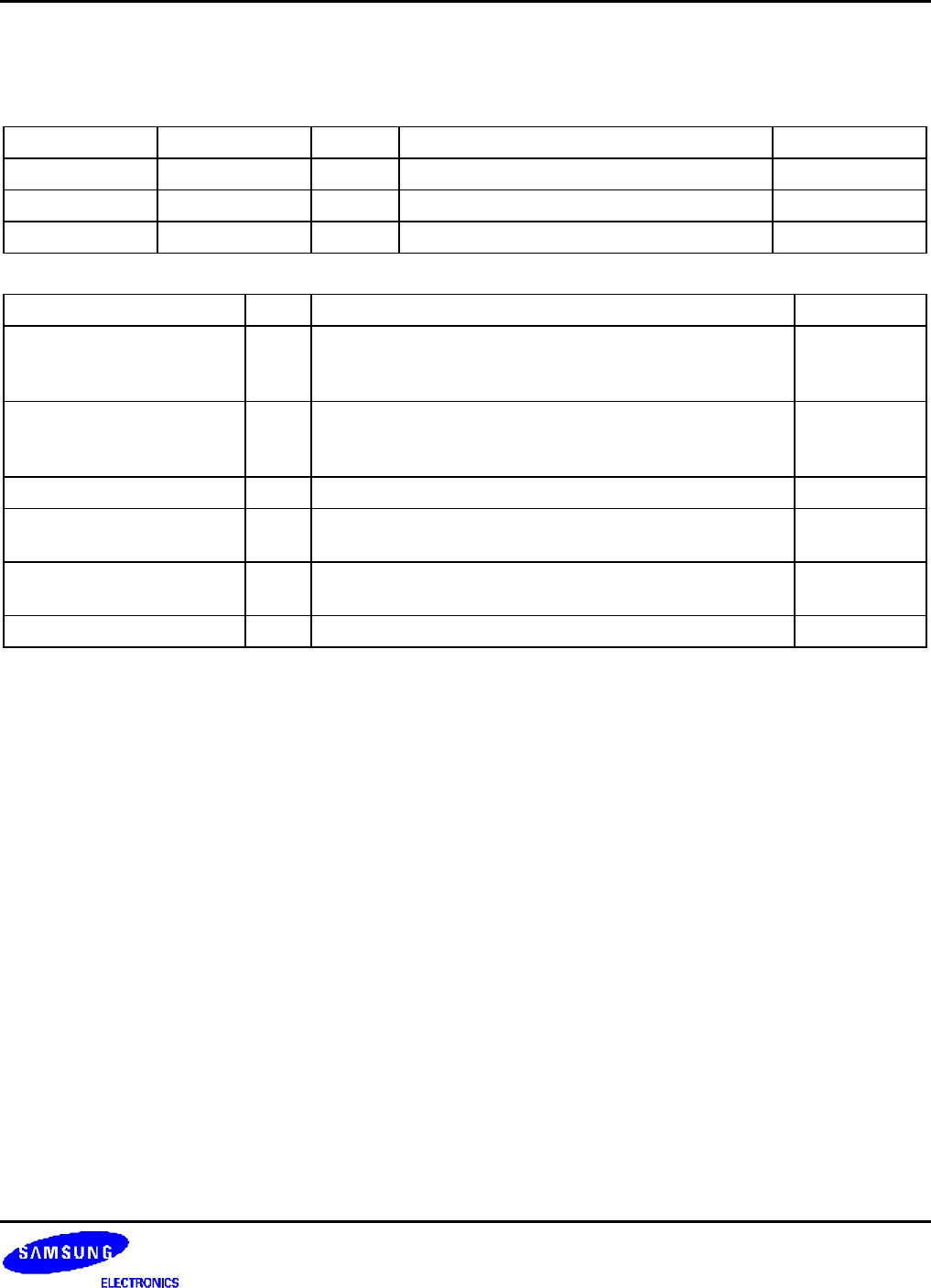

UART FIFO CONTROL REGISTER

There are three UART FIFO control registers including UFCON0, UFCON1 and UFCON2 in the UART block.

Register Address R/W Description Reset Value

UFCON0 0x50000008 R/W UART channel 0 FIFO control register 0x0

UFCON1 0x50004008 R/W UART channel 1 FIFO control register 0x0

UFCON2 0x50008008 R/W UART channel 2 FIFO control register 0x0

UFCONn Bit Description Initial State

Tx FIFO Trigger Level [7:6] Determine the trigger level of transmit FIFO.

00 = Empty 01 = 4-byte

10 = 8-byte 11 = 12-byte

00

Rx FIFO Trigger Level [5:4] Determine the trigger level of receive FIFO.

00 = 4-byte 01 = 8-byte

10 = 12-byte 11 = 16-byte

00

Reserved [3] 0

Tx FIFO Reset [2] Auto-cleared after resetting FIFO

0 = Normal 1= Tx FIFO reset

0

Rx FIFO Reset [1] Auto-cleared after resetting FIFO

0 = Normal 1= Rx FIFO reset

0

FIFO Enable [0] 0 = Disable 1 = Enable 0

NOTE: When the UART does not reach the FIFO trigger level and does not receive data during 3 word time in DMA receive

mode with FIFO, the Rx interrupt will be generated (receive time out), and the users should check the FIFO status

and read out the rest.