UART S3C2410A

11-6

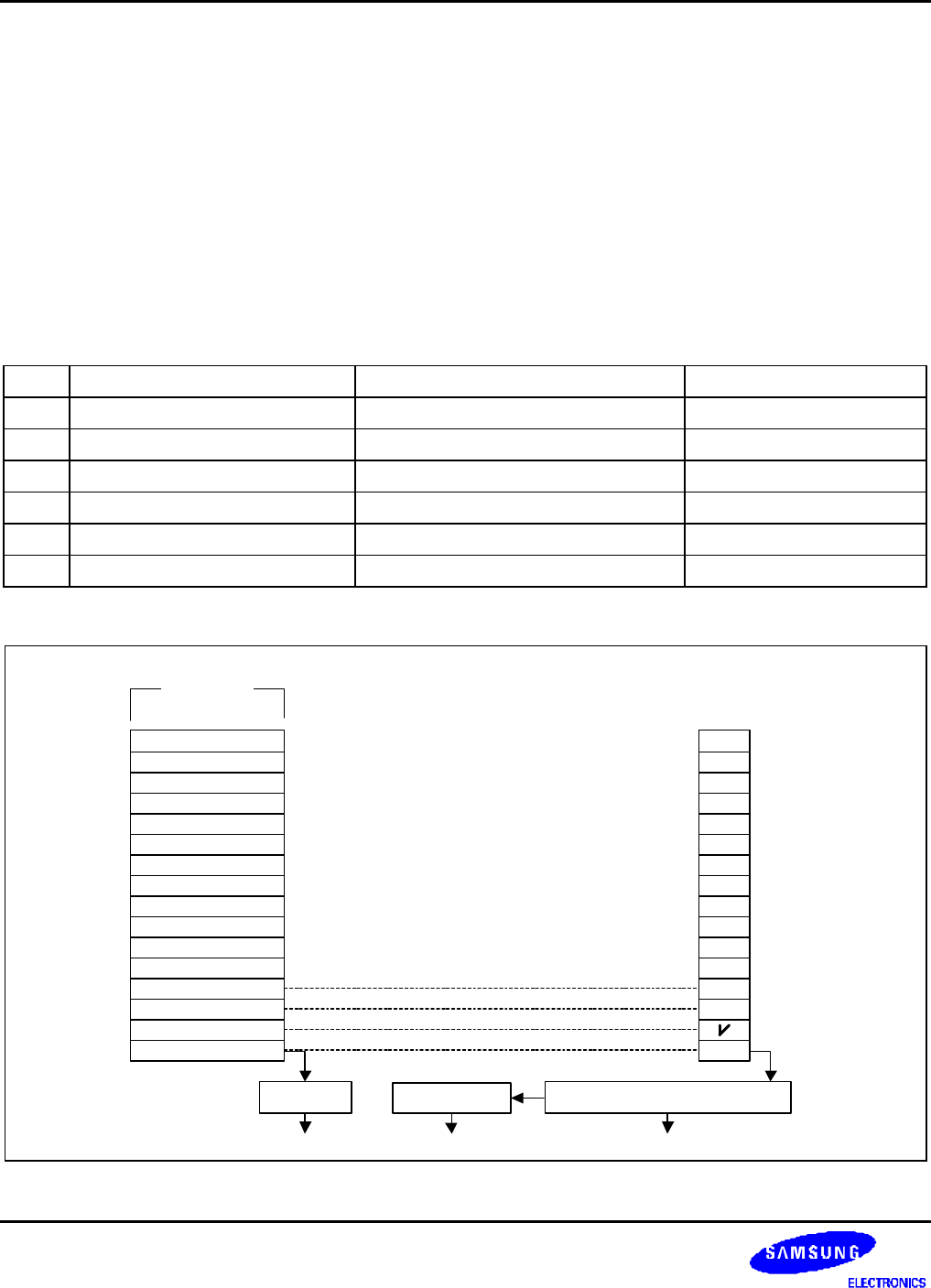

UART Error Status FIFO

UART has the error status FIFO besides the Rx FIFO register. The error status FIFO indicates which data, among

FIFO registers, is received with an error. The error interrupt will be issued only when the data, which has an error, is

ready to read out. To clear the error status FIFO, the URXHn with an error and UERSTATn must be read out.

For example,

It is assumed that the UART Rx FIFO receives A, B, C, and D characters sequentially and the frame error occurs

while receiving 'B'.

The actual UART receive error will not generate any error interrupt because the character, which was received with an

error, has not been read yet. The error interrupt will occur when the character is read out.

Figure 11-3 shows the UART receiving the four characters including the one error.

Time Sequence Flow Error Interrupt Note

#0 When no character is read out –

#1 A, B, C, and D is received –

#2 After A is read out The frame error (in B) interrupt occurs. The 'B' has to be read out.

#3 After B is read out –

#4 After C is read out –

#5 After D is read out –

-

-

-

-

-

-

-

-

-

-

-

'D'

'C'

'B'

'A'

RX-FIFO

Frame Error

URXHn Error Status Generator Unit

Error Status-FIFO

UERSTATn

-

Figure 11-3. UART Receiving 4 Characters with 1 Error