S3C2410A ARM INSTRUCTION SET

3-51

COPROCESSOR DATA OPERATIONS (CDP)

The instruction is only executed if the condition is true. The various conditions are defined in Table 3-2. The

instruction encoding is shown in Figure 3-25.

This class of instruction is used to tell a coprocessor to perform some internal operation. No result is communicated

back to ARM920T, and it will not wait for the operation to complete. The coprocessor could contain a queue of such

instructions awaiting execution, and their execution can overlap other activity, allowing the coprocessor and

ARM920T to perform independent tasks in parallel.

COPROCESSOR INSTRUCTIONS

The S3C2410A, unlike some other ARM-based processors, does not have an external coprocessor interface. It does

not have a on-chip coprocessor also.

So then all coprocessor instructions will cause the undefined instruction trap to be taken on the S3C2410A. These

coprocessor instructions can be emulated by the undefined trap handler. Even though external coprocessor can not

be connected to the S3C2410A, the coprocessor instructions are still described here in full for completeness.

(Remember that any external coprocessor described in this section is a software emulation.)

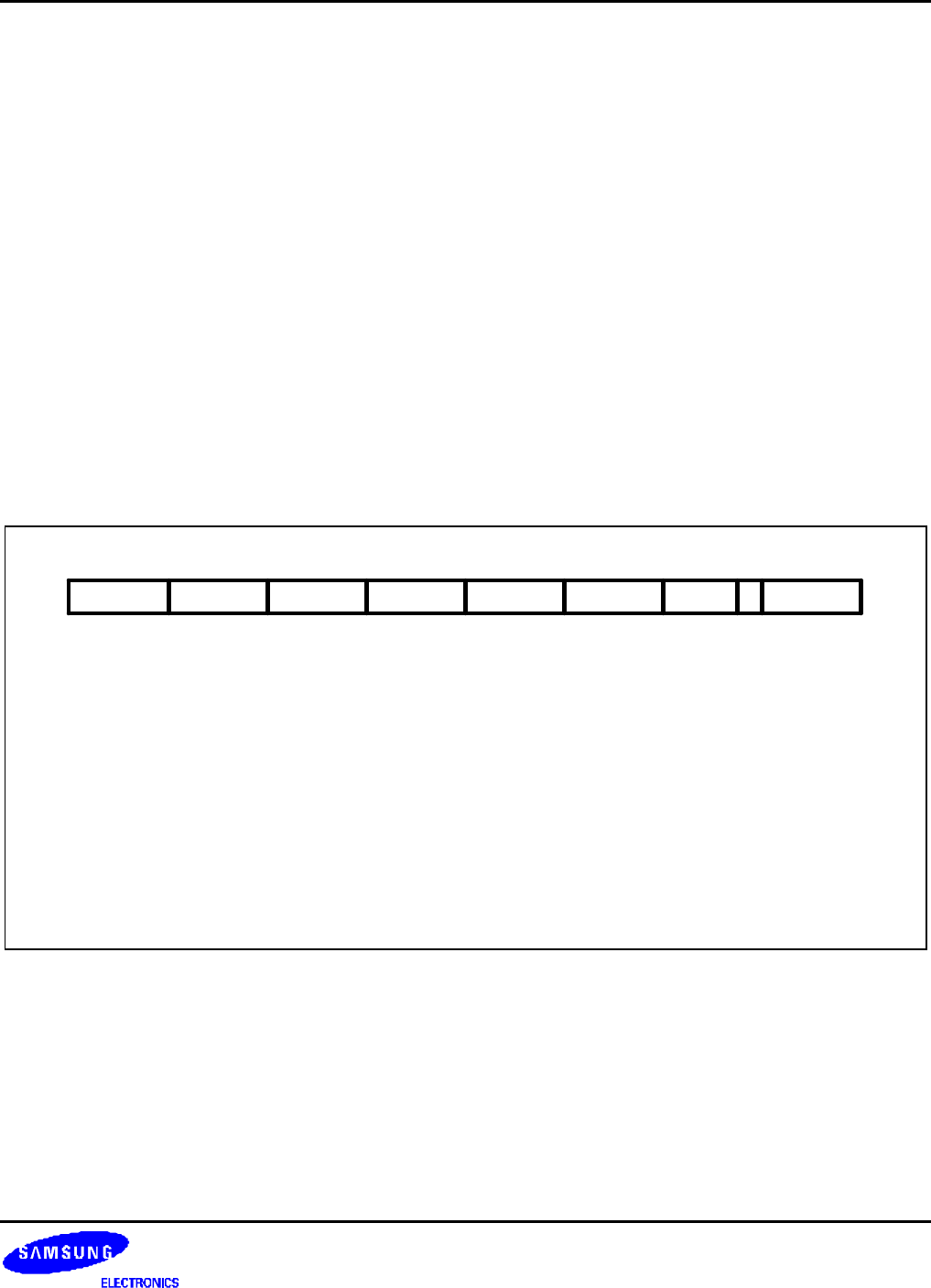

31 2427 19 15

Cond CRm

28 16 111223 20

[3:0] Coprocessor operand register

[7:5] Coprocessor information

[11:8] Coprocessor number

[15:12] Coprocessor destination register

[19:16] Coprocessor operand register

[23:20] Coprocessor operation code

[31:28] Condition Field

0CpCp#CRdCRn1110 CP Opc

8 7 5 4 3 0

Figure 3-25. Coprocessor Data Operation Instruction

Only bit 4 and bits 24 to 31 The coprocessor fields are significant to ARM920T. The remaining bits are used by

coprocessors. The above field names are used by convention, and particular coprocessors may redefine the use of

all fields except CP# as appropriate. The CP# field is used to contain an identifying number (in the range 0 to 15) for

each coprocessor, and a coprocessor will ignore any instruction which does not contain its number in the CP# field.

The conventional interpretation of the instruction is that the coprocessor should perform an operation specified in the

CP Opc field (and possibly in the CP field) on the contents of CRn and CRm, and place the result in CRd.