ARM INSTRUCTION SET S3C2410A

3-34

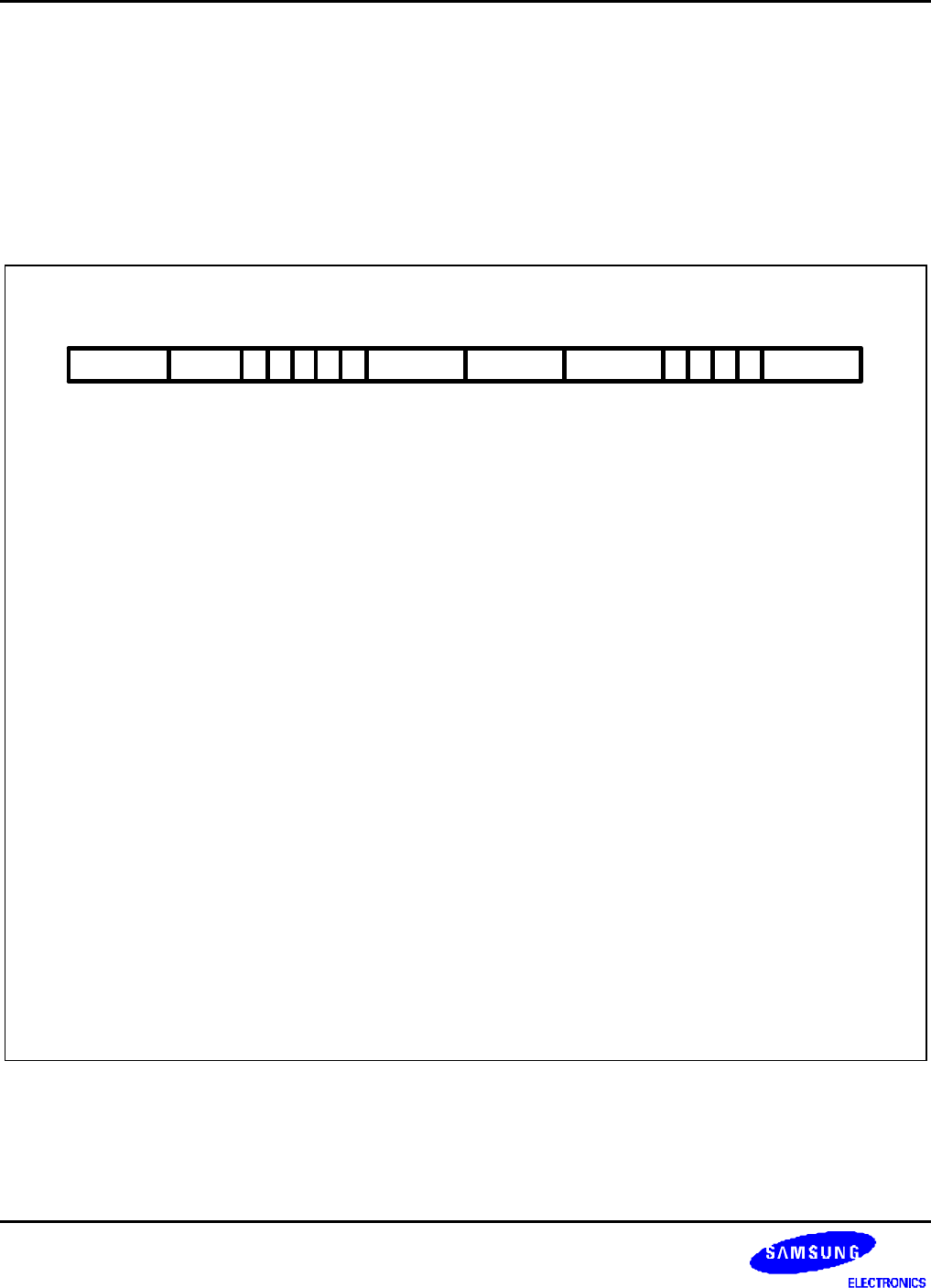

HALFWORD AND SIGNED DATA TRANSFER (LDRH/STRH/LDRSB/LDRSH)

The instruction is only executed if the condition is true. The various conditions are defined in Table 3-2. The

instruction encoding is shown in Figure 3-16.

These instructions are used to load or store half-words of data and also load sign-extended bytes or half-words of

data. The memory address used in the transfer is calculated by adding an offset to or subtracting an offset from a

base register. The result of this calculation may be written back into the base register if auto-indexing is required.

31 27 19 15

Cond

28 16 11122123

0

20

L Rn Rd

[3:0] Offset Register

[6][5] S H

0 0 = SWP instruction

0 1 = Unsigned halfword

1 1 = Signed byte

1 1 = Signed halfword

[15:12] Source/Destination Register

[19:16] Base Register

[20] Load/Store

0 = Store to memory

1 = Load from memory

[21] Write-back

0 = No write-back

1 = Write address into base

[23] Up/Down

0 = Down: subtract offset from base

1 = Up: add offset to base

[24] Pre/Post Indexing

0 = Post: add/subtract offset after transfer

1 = Pre: add/subtract offset bofore transfer

[31:28] Condition Field

22

000 P U 0000W

2425

1 RmS H 1

8 7 6 5 4 3 0

Figure 3-16. Halfword and Signed Data Transfer with Register Offset