S3C2410A ARM INSTRUCTION SET

3-11

CPSR FLAGS

The data processing operations may be classified as logical or arithmetic. The logical operations (AND, EOR, TST,

TEQ, ORR, MOV, BIC, MVN) perform the logical action on all corresponding bits of the operand or operands to

produce the result. If the S bit is set (and Rd is not R15, see below) the V flag in the CPSR will be unaffected, the C

flag will be set to the carry out from the barrel shifter (or preserved when the shift operation is LSL #0), the Z flag will

be set if and only if the result is all zeros, and the N flag will be set to the logical value of bit 31 of the result.

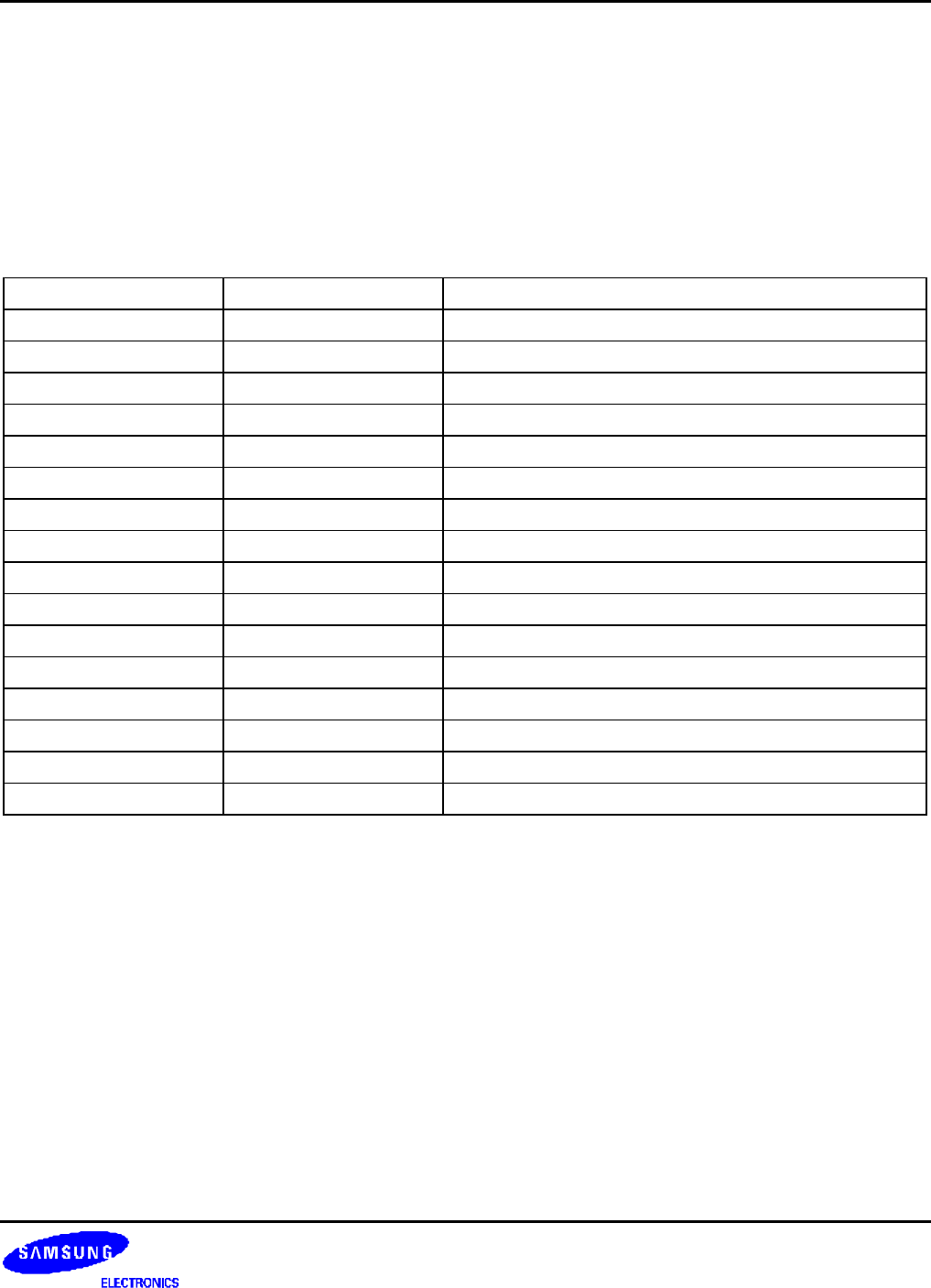

Table 3-3. ARM Data Processing Instructions

Assembler Mnemonic OP Code Action

AND 0000 Operand1 AND operand2

EOR 0001 Operand1 EOR operand2

WUB 0010 Operand1 - operand2

RSB 0011 Operand2 operand1

ADD 0100 Operand1 + operand2

ADC 0101 Operand1 + operand2 + carry

SBC 0110 Operand1 - operand2 + carry - 1

RSC 0111 Operand2 - operand1 + carry - 1

TST 1000 As AND, but result is not written

TEQ 1001 As EOR, but result is not written

CMP 1010 As SUB, but result is not written

CMN 1011 As ADD, but result is not written

ORR 1100 Operand1 OR operand2

MOV 1101 Operand2 (operand1 is ignored)

BIC 1110 Operand1 AND NOT operand2 (Bit clear)

MVN 1111 NOT operand2 (operand1 is ignored)

The arithmetic operations (SUB, RSB, ADD, ADC, SBC, RSC, CMP, CMN) treat each operand as a 32 bit integer

(either unsigned or 2's complement signed, the two are equivalent). If the S bit is set (and Rd is not R15) the V flag in

the CPSR will be set if an overflow occurs into bit 31 of the result; this may be ignored if the operands were

considered unsigned, but warns of a possible error if the operands were 2's complement signed. The C flag will be

set to the carry out of bit 31 of the ALU, the Z flag will be set if and only if the result was zero, and the N flag will be

set to the value of bit 31 of the result (indicating a negative result if the operands are considered to be 2's

complement signed).