ARM INSTRUCTION SET S3C2410A

3-2

NOTE

Some instruction codes are not defined but do not cause the Undefined instruction trap to be taken, for

instance a Multiply instruction with bit 6 changed to a 1. These instructions should not be used, as their

action may change in future ARM implementations.

INSTRUCTION SUMMARY

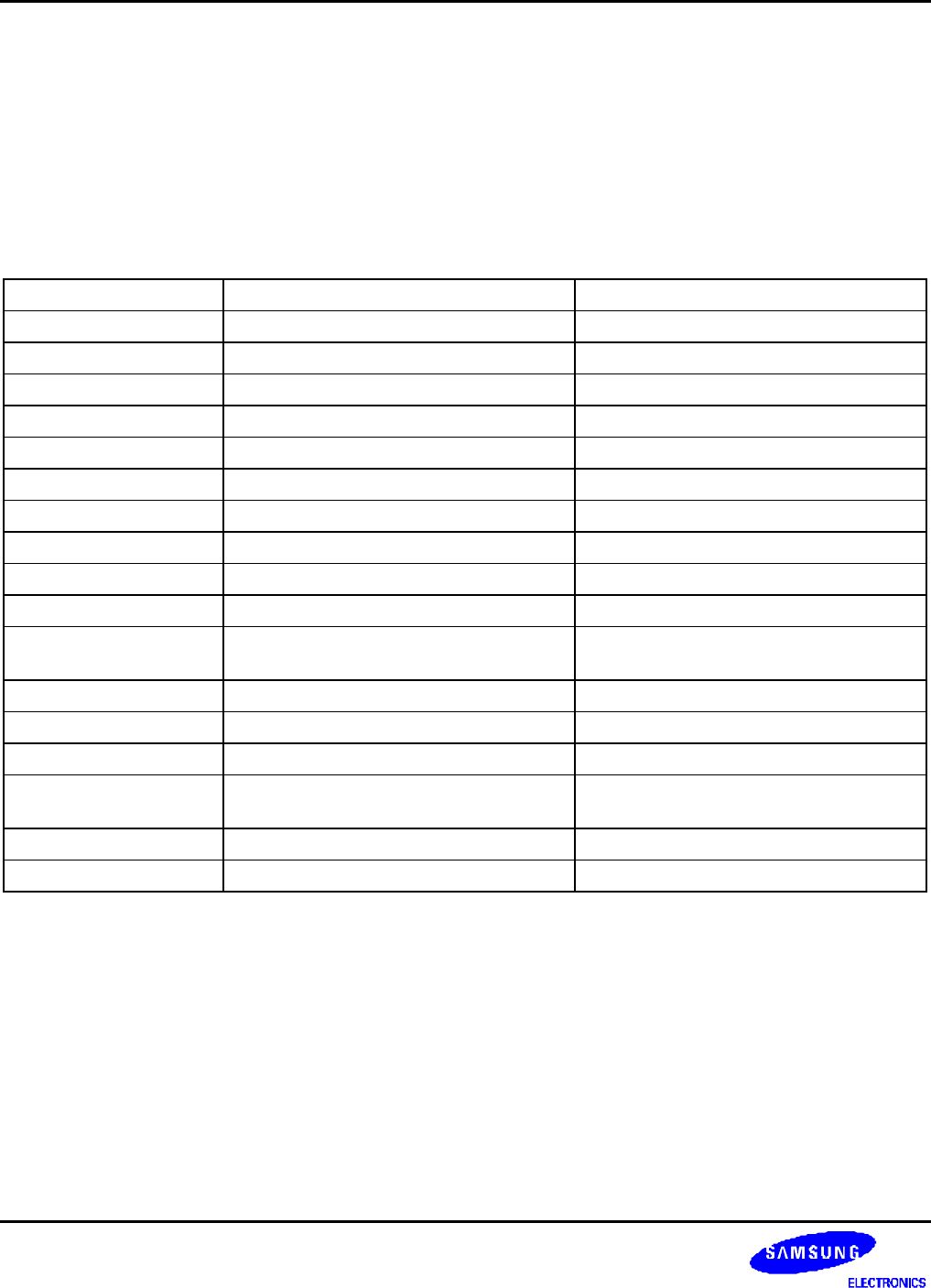

Table 3-1. The ARM Instruction Set

Mnemonic Instruction Action

ADC Add with carry Rd: = Rn + Op2 + Carry

ADD Add Rd: = Rn + Op2

AND AND Rd: = Rn AND Op2

B Branch R15: = address

BIC Bit Clear Rd: = Rn AND NOT Op2

BL Branch with Link R14: = R15, R15: = address

BX Branch and Exchange R15: = Rn, T bit: = Rn[0]

CDP Coprocessor Data Processing (Coprocessor-specific)

CMN Compare Negative CPSR flags: = Rn + Op2

CMP Compare CPSR flags: = Rn - Op2

EOR Exclusive OR Rd: = (Rn AND NOT Op2)

OR (Op2 AND NOT Rn)

LDC Load coprocessor from memory Coprocessor load

LDM Load multiple registers Stack manipulation (Pop)

LDR Load register from memory Rd: = (address)

MCR Move CPU register to coprocessor

register

cRn: = rRn {<op>cRm}

MLA Multiply Accumulate Rd: = (Rm × Rs) + Rn

MOV Move register or constant Rd: = Op2