DMA S3C2410A

8-10

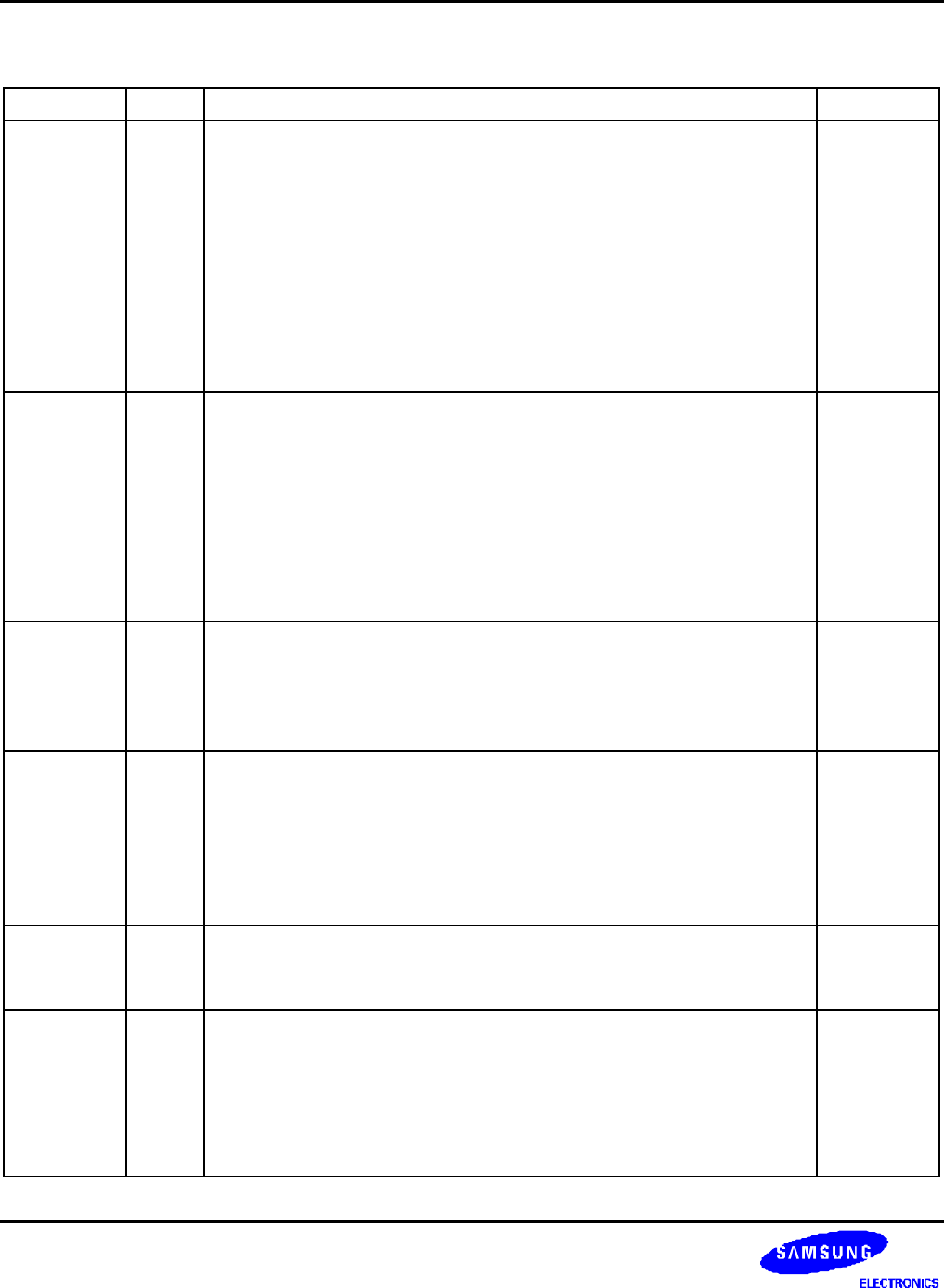

DMA CONTROL (DCON) REGISTER (Continued)

DCONn Bit Description Initial State

SERVMODE [27] Select the service mode between Single service mode and Whole service

mode.

0: Single service mode is selected in which after each atomic transfer

(single or burst of length four) DMA stops and waits for another DMA

request.

1: Whole service mode is selected in which one request gets atomic

transfers to be repeated until the transfer count reaches to 0. In this mode,

additional request are not required.

Note that even in the Whole service mode, DMA releases the bus after

each atomic transfer and then tries to re-get the bus to prevent starving of

other bus masters.

0

HWSRCSEL [26:24] Select DMA request source for each DMA.

DCON0: 000:nXDREQ0 001:UART0 010:SDI 011:Timer 100:USB device EP1

DCON1: 000:nXDREQ1 001:UART1 010:I2SSDI 011:SPI 100:USB device EP2

DCON2: 000:I2SSDO 001:I2SSDI 010:SDI 011:Timer 100:USB device EP3

DCON3: 000:UART2 001:SDI 010:SPI 011:Timer 100:USB device EP4

These bits control the 4-1 MUX to select the DMA request source of each

DMA. These bits have meanings only if H/W request mode is selected by

DCONn[23].

00

SWHW_SEL [23] Select the DMA source between software (S/W request mode) and

hardware (H/W request mode).

0: S/W request mode is selected and DMA is triggered by setting

SW_TRIG bit of DMASKTRIG control register.

1: DMA source selected by bit[26:24] triggers the DMA operation.

0

RELOAD [22] Set the reload on/off option.

0: auto reload is performed when a current value of transfer count

becomes 0 (i.e. all the required transfers are performed).

1: DMA channel (DMA REQ) is turned off when a current value of

transfer count becomes 0. The channel on/off bit (DMASKTRIGn[1]) is

set to 0 (DREQ off) to prevent unintended further start of new DMA

operation.

0

DSZ [21:20] Data size to be transferred.

00 = Byte 01 = Half word

10 = Word 11 = reserved

00

TC [19:0] Initial transfer count (or transfer beat).

Note that the actual number of bytes that are transferred is computed by

the following equation: DSZ x TSZ x TC. Where, DSZ, TSZ (1 or 4), and

TC represent data size (DCONn[21:20]), transfer size (DCONn[28]), and

initial transfer count, respectively.

This value will be loaded into CURR_SRC only if the CURR_SRC is 0 and

the DMA ACK is 1.

00000