S3C2410A MEMORY CONTROLLER

5-19

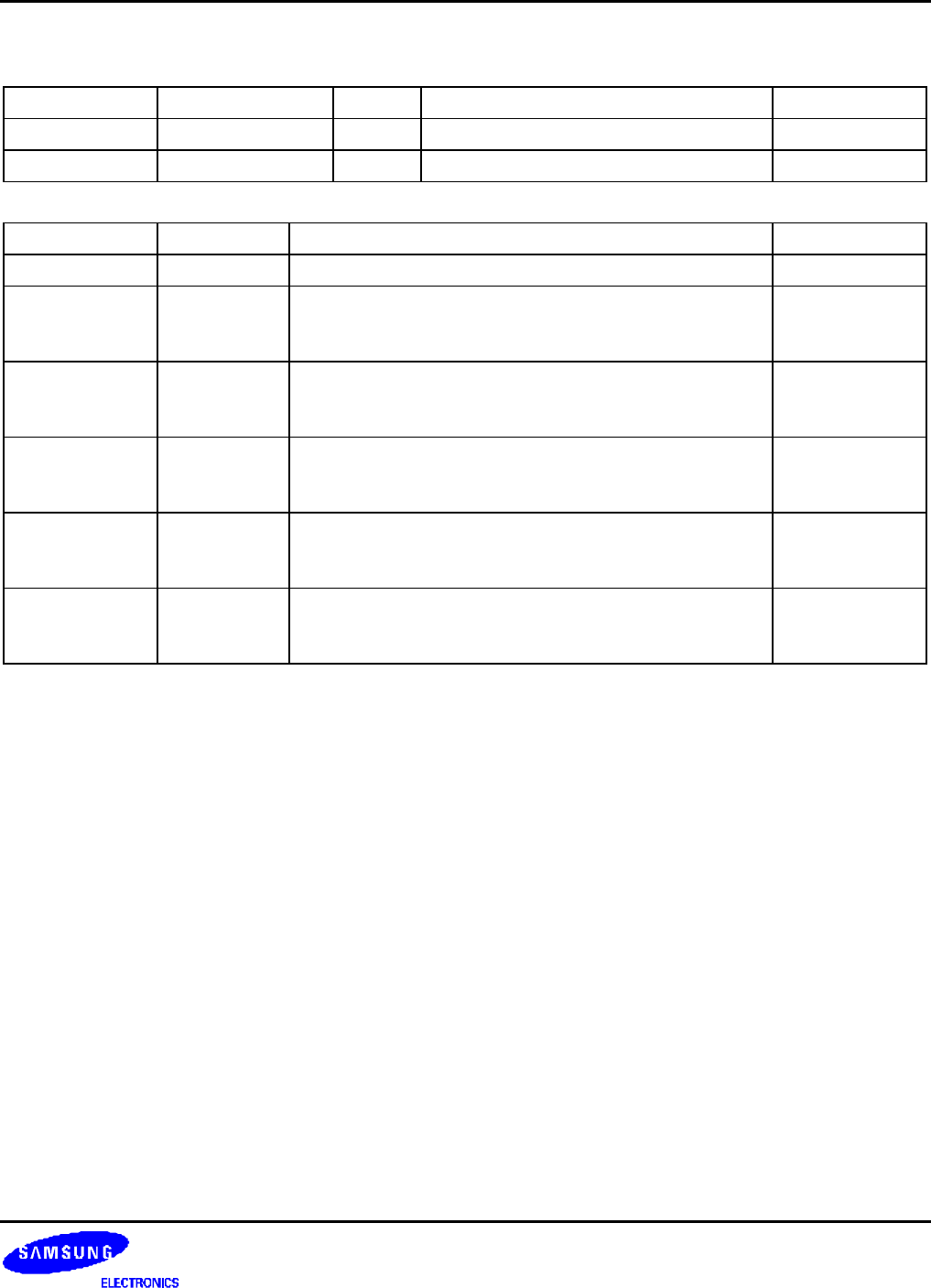

SDRAM MODE REGISTER SET REGISTER (MRSR)

Register Address R/W Description Reset Value

MRSRB6 0x4800002C R/W Mode register set register bank6 xxx

MRSRB7 0x48000030 R/W Mode register set register bank7 xxx

MRSR Bit Description Initial State

Reserved [11:10] Not used –

WBL [9] Write burst length

0: Burst (Fixed)

1: Reserved

x

TM [8:7] Test mode

00: Mode register set (Fixed)

01, 10 and 11: Reserved

xx

CL [6:4] CAS latency

000 = 1 clock, 010 = 2 clocks, 011=3 clocks

Others: reserved

xxx

BT [3] Burst type

0: Sequential (Fixed)

1: Reserved

x

BL [2:0] Burst length

000: 1 (Fixed)

Others: Reserved

xxx

NOTE: MRSR register must not be reconfigured while the code is running on SDRAM.

IMPORTANT NOTES

In Power_OFF mode, SDRAM has to enter SDRAM self-refresh mode.