USB DEVICE S3C2410A

13-14

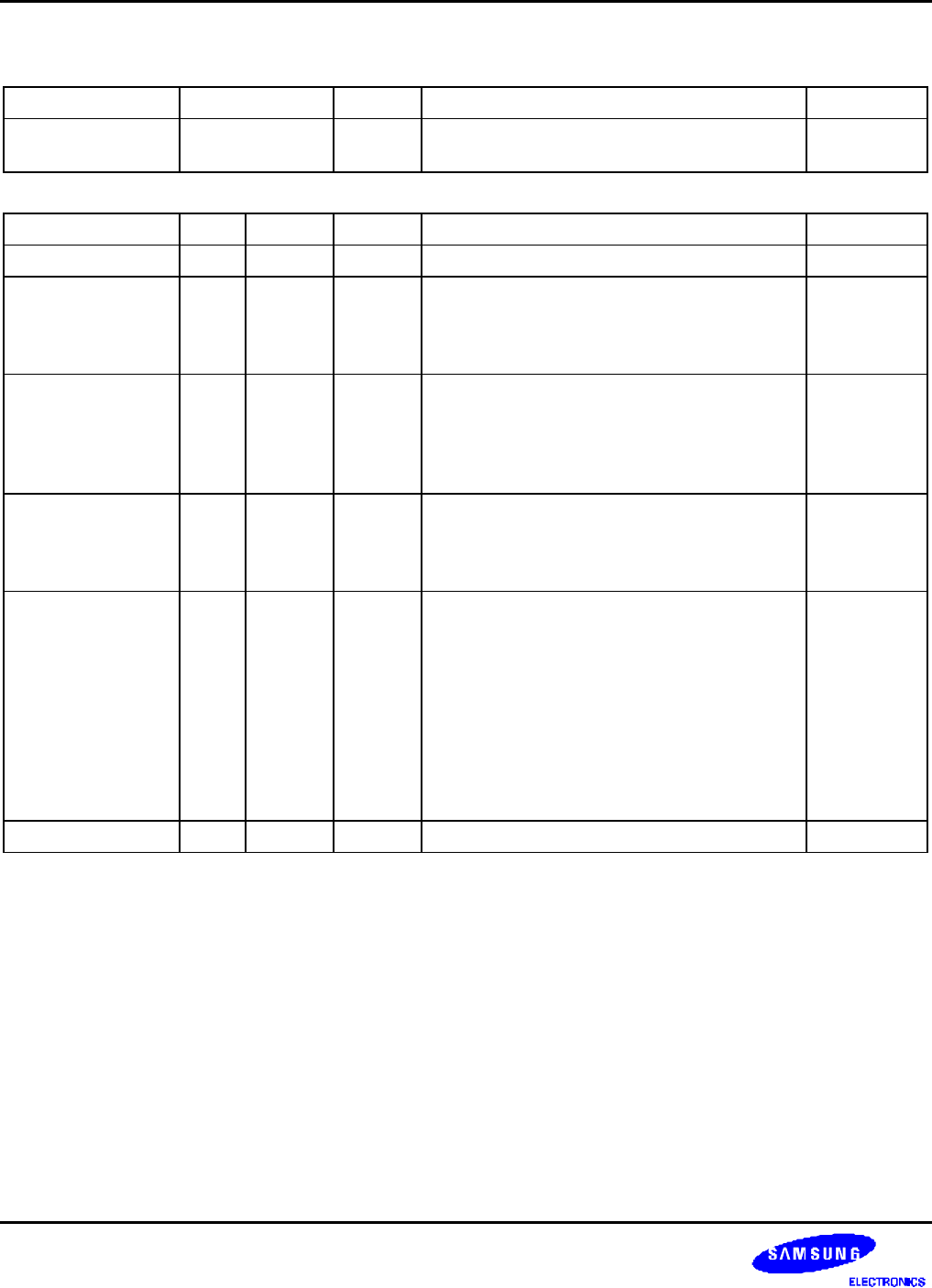

END POINT IN CONTROL STATUS REGISTER (IN_CSR1_REG/IN_CSR2_REG)

Register Address R/W Description Reset Value

IN_CSR1_REG 0x52000184(L)

0x52000187(B)

R/W

(byte)

IN END POINT control status register1 0x00

IN_CSR1_REG Bit MCU USB Description Initial State

Reserved [7] – – – 0

CLR_DATA_

TOGGLE

[6] R/W R/

CLEAR

Used in Set-up procedure.

0: There are alternation of DATA0 and DATA1

1: The data toggle bit is cleared and PID in

packet will maintain DATA0

0

SENT_STALL [5] R/

CLEAR

SET Set by the USB when an IN token issues a

STALL handshake, after the MCU sets

SEND_STALL bit to start STALL handshaking.

When the USB issues a STALL handshake,

IN_PKT_RDY is cleared

0

SEND_STALL [4] W/R R 0: The MCU clears this bit to finish the

STALL condition.

1: The MCU issues a STALL handshake to

the USB.

0

FIFO_FLUSH [3] R/W CLEAR Set by the MCU if it intends to flush the

packet in Input-related FIFO. This bit is

cleared by the USB when the FIFO is flushed.

The MCU is interrupted when this happens. If

a token is in process, the USB waits until the

transmission is complete before FIFO flushing.

If two packets are loaded into the FIFO, only

first packet (The packet is intended to be sent

to the host) is flushed, and the corresponding

IN_PKT_RDY bit is cleared

0

Reserved [2:1] – – – 0